Aktivering af NVMe SSD-grænsefladen på et Xilinx ZCU102-evalueringssæt

Bidraget af DigiKeys nordamerikanske redaktører

2020-05-12

Oversigt

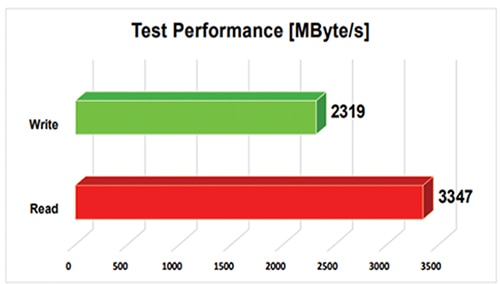

Zynq® UltraScale+™ MPSoC-familien, der er baseret på Xilinx®UltraScale™ MPSoC-arkitekturen, integrerer et 64-bit quad-core- eller dual-core ARM-baseret processorsystem (PS) med 64 bit og Xilinx' programmerbar logik (PL) UltraScale-arkitektur i en enkelt enhed. Der er også indbygget on-chip-hukommelse, eksterne multiport-hukommelsesinterfaces og et rigt sæt af perifere forbindelsesinterfaces, især en GTH 16,3 Gbps transceiver, som har mulighed for at understøtte en PCI Express® Gen3-lagerenhedsgrænseflade, f.eks. et NVMe SSD-drev. Denne artikel demonstrerer løsningen af implementeringen af NVMe SSD-grænsefladen (solid state drive) på Xilinx' ZCU102 Evaluation Kit ved hjælp af Design Gateway's NVMeG3-IP Core, som er i stand til at opnå en utrolig hurtig ydeevne: 2.319 MB/s skrivehastighed og 3.347 MB/s læsehastighed.

Introduktion til Zynq® UltraScale+ MPSoC ZCU102-evalueringssættet

ZCU102 er et generelt evalueringskort til hurtig prototyping baseret på XCZU9EG-2FFVB1156E MPSoC-enheden. Kortet indeholder en højhastigheds DDR4 SODIMM og komponenthukommelsesinterfaces, FMC-udvidelsesporte, serielle transceivere med flere gigabit pr. sekund, en række perifere grænseflader og FPGA-logik til brugertilpassede designs, hvilket alt sammen giver en fleksibel prototypeplatform.

Figur 1: ZCU102-evalueringssæt. (Billedkilde: Xilinx Inc.)

Figur 1: ZCU102-evalueringssæt. (Billedkilde: Xilinx Inc.)

ZCU102 giver programmerbare logikfunktioner til at skabe avancerede applikationer som f.eks. 5G Wireless, næste generation af avancerede ADAS-systemer (Advanced Driver Assistance Systems) og IIoT-løsninger (Industrial Internet of Things).

Til applikationer, der kræver ekstern datalagring med høj ydeevne og høj pålidelighed, f.eks. NVMe SSD-drev, er der under alle omstændigheder brug for den rigtige løsning, der udnytter GTH Transceiver for PCI Express® Gen3 compliance interface.

Introduktion til NVMe SSD-lagring

NVM Express (NVMe) definerer grænsefladen for værtscontrolleren til at få adgang til SSD'er via PCI Express. NVM Express optimerer udstedelsen af kommandoen og færdiggørelsesprocessen ved kun at bruge to registre (Command issue og Command completion). Ellers understøtter NVMe parallel drift ved at understøtte op til 64K kommandoer i en enkelt kø. 64K kommandoposter forbedrer overførselsydelsen for både sekventiel og tilfældig adgang.

NVMe-drev har banet vejen for datalagring og databehandling ved meget høje hastigheder. Ved at bruge PCIe Express® Gen3-teknologi kan moderne NVMe SSD-drev opnå hastigheder på helt op til 40 Gbit/s spidsydelse.

Et eksempel på en NVMe-lagerenhed er vist her.

Implementering af NVMe-værtscontroller på ZCU102

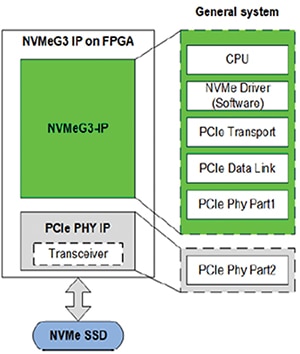

Figur 2: NVMe-implementering. (Billedkilde: Design Gateway)

Figur 2: NVMe-implementering. (Billedkilde: Design Gateway)

Konventionelt implementeres NVMe-værten ved hjælp af en værtsprocessor, der fungerer sammen med en PCIe-controller til overførsel af data til og fra NVMe SSD'en. NVMe-protokollen er implementeret til enhedsdriverkommunikation med PCIe-controllerens hardware CPU-periferiudstyr, der er forbundet via en bus med meget høj hastighed. Ekstern DDR-hukommelse er nødvendig til datapuffering og kommandokø for at overføre data mellem PCIe-controlleren og SSD'en.

Da en PCIe Gen3 Integrated Block ikke er tilgængelig på en XCZU9EG-2FFVB1156E FPGA-enhed på ZCU102, er det ikke muligt at anvende en konventionel implementeringsmetode.

Design Gateway foreslår en løsning ved at bruge NVMeG3-IP Core, som vist i figur 2, til at aktivere en NVMe SSD-grænseflade til en Zynq® UltraScale+™ MPSoC-enhed, hvor der ikke er en PCIe-integreret blok til rådighed. NVMe-grænsefladen til ZCU102 gør det muligt at opbygge et multikanal-RAID-system med meget høj ydeevne og det lavest mulige FPGA-ressourceforbrug. NVMeG3-IP-kernelicensen omfatter et eksempel på et referencedesign, der hjælper designere med at reducere udviklingstiden og omkostningerne.

Oversigt over Design Gateway's NVMeG3-IP

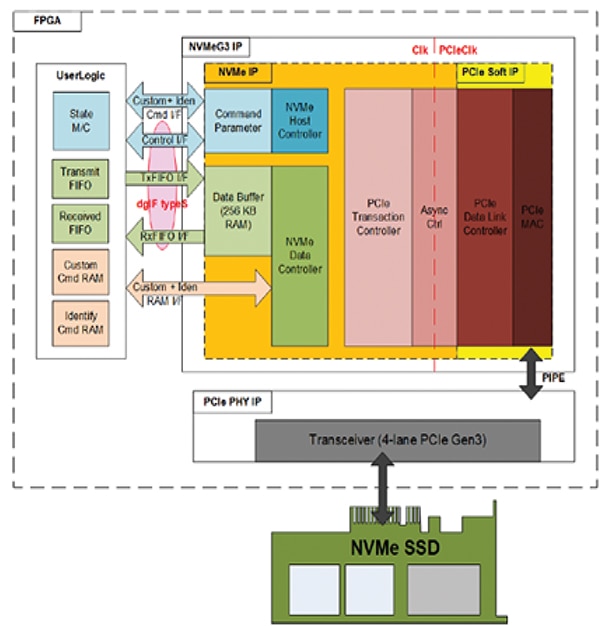

NVMe IP Core med PCIe Gen3 Soft IP (NVMeG3-IP) er ideel til at få adgang til en NVMe SSD uden en PCIe integreret blok, CPU og ekstern hukommelse. NVMeG3-IP omfatter PCIe Gen3 Soft IP og 256 Kbyte hukommelse. Denne løsning anbefales til applikationer, der kræver NVMe SSD-lagring med ultrahøjhastighedsydelse ved hjælp af en billig FPGA, som ikke indeholder en PCIe-integreret blok.

Figur 3: NVMeG3-IP-blokdiagram. (Billedkilde: Design Gateway)

Figur 3: NVMeG3-IP-blokdiagram. (Billedkilde: Design Gateway)

NVMeG3-IP's funktioner

NVMeG3-IP har mange funktioner, hvoraf nogle er fremhævet nedenfor:

- Implementer applikationslag, transaktionslag, datalinklag og nogle dele af det fysiske lag til at få adgang til NVMe SSD'en uden CPU-forbrug

- Operere med Xilinx PCIe PHY IP konfigureret som en 4-lane PCIe Gen3 (128-bit busgrænseflade)

- Inkluderer 256 Kbyte RAM-datapuffer

- Enkel brugergrænseflade via dgIF typeS

- Understøtter seks kommandoer, dvs. identificere, lukke ned, skrive, læse, SMART og skylle (understøtter yderligere kommandoer som valgfri)

- Understøttet NVMe-enhed:

- Grundklassekode:01h (masselagring), underklassekode:08h (ikke-flygtig), programmeringsgrænseflade:02h (NVMHCI)

- MPSMIN (Memory Page Size Minimum): 0 (4Kbyte)

- MDTS (maksimal dataoverførselsstørrelse): Mindst 5 (128 Kbyte) eller 0 (ingen begrænsning)

- LBA-enhed: 512 byte eller 4096 byte

- Brugerens clockfrekvens skal være større end eller lig med PCIe-uret (250 MHz for Gen3)

- Tilgængeligt referencedesign:

- ZCU102 med AB17-M2FMC-adapterkort

- KCU105 med AB18-PCIeX16/AB16-PCIeXOVR-adapterkort

- VCU118 med AB18-PCIeX16-adapterkort

Design Gateway har udviklet NVMeG3-IP til at køre som en NVMe-værtscontroller til at få adgang til en NVMe SSD. Brugergrænsefladen og standardfunktionerne er designet til nem brug uden at du behøver at kende NVMe-protokollen. Den yderligere funktion i NVMeG3-IP er den indbyggede PCIe soft IP, som implementerer dataforbindelseslaget og nogle dele af det fysiske lag i PCIe-protokollen ved hjælp af ren logik. Så NVMeG3-IP kan køre i en FPGA, som ikke har en PCIe-integreret blok, ved at bruge indbygget PCIe soft IP og Xilinx PCIe PHY IP-kernen. Xilinx PCIe PHY IP er en gratis IP-kerne, som omfatter en transceiver og en logisk equalizer.

NVMeG3-IP understøtter seks NVMe-kommandoer, dvs. Identificere, Luk ned, Skriv, Læs, SMART og Skyl. 256 Kbyte BlockRAM er integreret i NVMeG3-IP til at fungere som datapuffer. Systemet har ikke brug for en CPU og ekstern hukommelse. Flere detaljer om NVMeG3-IP er beskrevet i databladet, som kan downloades fra vores websted.

FPGA-ressourceforbruget på XCZU9EG-2FFVB1156E FPGA-enheden er vist i tabel 1 nedenfor.

|

Tabel 1: Eksempel på implementeringsstatistikker for Ultrascale/Ultrascale+-enheden

Implementering og resultat af ydeevne på ZCU102

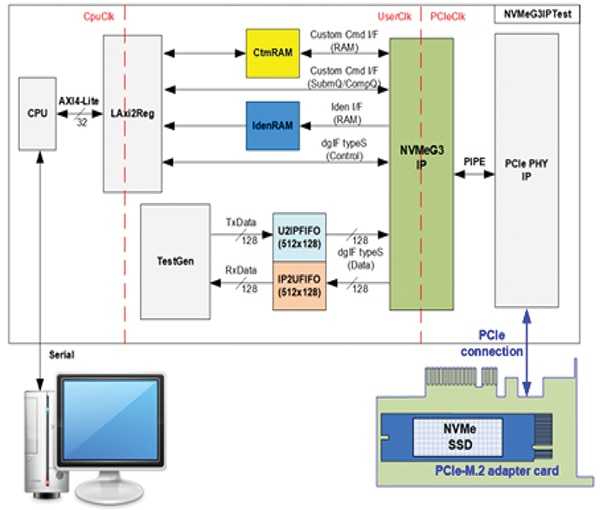

Figur 4 viser en oversigt over referencedesignet baseret på ZCU102 til demonstration af NVMeG3-IP-drift. NVMeG3IPTest-modulet i demosystemet omfatter følgende moduler: TestGen, LAxi2Reg, CtmRAM, IdenRAM og FIFO.

For flere detaljer om NVMeG3-IP-referencedesignet henvises til dokumentet om NVMeG3-IP-referencedesignet på Design Gateway's websted.

Figur 4: Oversigt over NVMeG3-IP-referencedesign. (Billedkilde: Design Gateway)

Figur 4: Oversigt over NVMeG3-IP-referencedesign. (Billedkilde: Design Gateway)

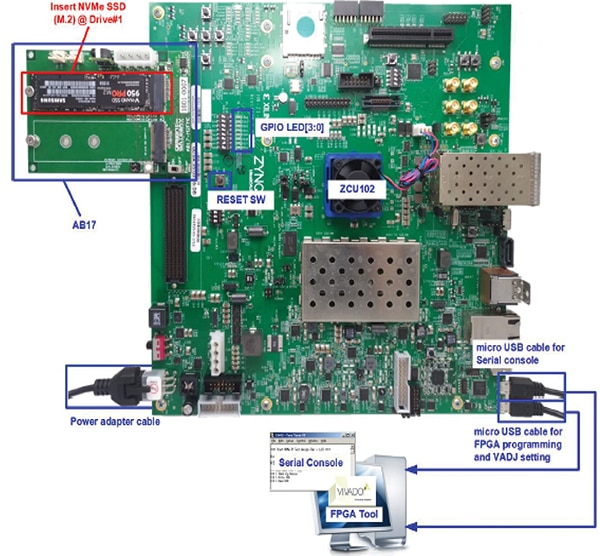

Demosystemet er designet til at skrive/verificere data med NVMe SSD'en på ZCU102. Brugeren styrer testoperationen via en seriel konsol. For at NVMe SSD'en kan interfacet med ZCU102, kræves der et AB17-M2FMC-adapterkort som vist i figur 5.

Figur 5: NVMeG3-IP-demomiljø opsat på ZCU102. (Billedkilde: Design Gateway)

Figur 5: NVMeG3-IP-demomiljø opsat på ZCU102. (Billedkilde: Design Gateway)

Eksempel på testresultatet ved at køre demosystemet på ZCU102 med 512 GB Samsung 970 Pro er vist i figur 6.

Figur 6: NVMe SSD læse-/skriveydelse på ZCU102 ved brug af Samsung 970 PRO S. (Billedkilde: Design Gateway)

Figur 6: NVMe SSD læse-/skriveydelse på ZCU102 ved brug af Samsung 970 PRO S. (Billedkilde: Design Gateway)

Konklusion

NVMeG3-IP Core er en løsning til aktivering af NVMe SSD-interface på ZCU102-evalueringssættet og også en løsning til Xilinx®'s Zynq® UltraScale+™ MPSoC-enhedsfamilie, hvor en integreret PCIe-blok ikke er tilgængelig. NVMeG3-IP er designet med det formål at opnå den højest mulige ydelse med det lavest mulige FPGA ressourceforbrug til NVMe SSD-adgang uden brug af en CPU. Den er meget velegnet til højtydende NVMe-lagring uden CPU-opfindelse og er i stand til at implementere flere NVMe SSD-grænseflader ved at udnytte GTH-transceivere uden begrænsninger fra antallet af tilgængelige PCIe-integrerede blokke på FPGA-enheden.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.