Grundlæggende om FPGA'er – del 4: Sådan kommer du i gang med Xilinx FPGA'er

Bidraget af DigiKeys nordamerikanske redaktører

2020-04-01

Redaktørens note: Optimale behandlingsløsninger leveres ofte af kombinationer af RISC, CISC, grafikprocessorer og FPGA'er, FPGA'er på egen hånd eller af FPGA'er, der kan prale af hårde processorkerner som en del af deres struktur. Imidlertid er mange designere ikke bekendt med FPGA'ers funktionaliteter, hvordan de har udviklet sig, og hvordan de bruges. Del 1 af denne serie i flere dele indeholder en introduktion til FPGA'er på højt niveau, del 2 fokuserede på FPGA-tilbud fra Lattice Semiconductor, og del 3 koncentrerede sig om FPGA-enhedsfamilier og designværktøjer fra Microchip Technology (fra dennes datterselskab Microsemi Corporation). Her i del 4 beskrives komponenterne og værktøjerne fra Xilinx. I del 5 beskrives tilbuddene fra Altera.

Som drøftet i del 1 har feltprogrammerbare gate arrays (FPGA'er) mange egenskaber, der gør dem til et uvurderligt computeraktiv, enten anvendt separat eller i en heterogen arkitektur, men mange udviklere er ikke bekendt med FPGA'er, og hvordan de kan integrere disse enheder i deres design.

En måde at løse denne udfordring på er at se mere indgående på FPGA-arkitekturer og tilknyttede værktøjer fra større leverandører. Denne artikel kigger på sortimentet fra Xilinx.

Oversigt over FPGA-muligheder på højt niveau

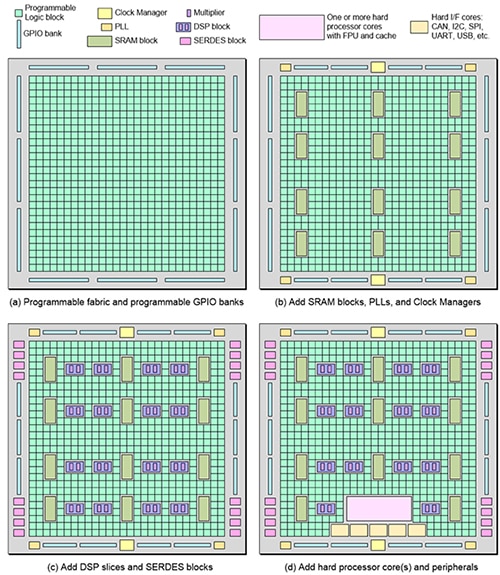

Der er mange forskellige typer FPGA'er på markedet, hver med forskellige kombinationer af egenskaber og funktioner. Den programmerbare struktur udgør hjertet i enhver FPGA. Dette præsenteres som en række programmerbare logikblokke, også kendt som logiske elementer (LE'er) (figur 1a). Det næste trin op i FPGA-strukturen er at inkludere ting såsom SRAM-blokke, kaldet "block RAM" (BRAM), PLL'er (Phase Lock Loops) og clock-managers (figur 1b). Digitale signalbehandlingsblokke (DSP) (kaldet DSP-skiver) og high-speed-blokke med serialiseringsfunktion/serie-parallel omsætter (SERDES) kan også tilføjes (figur 1c).

Figur 1: De enkleste FPGA'er indeholder kun programmerbar struktur og konfigurerbar IO (GPIO) (a). Forskellige arkitekturer forstærker denne grundlæggende struktur med SRAM-blokke, PLL'er og clock-managers (b), DSP-blokke og SERDES-interfaces (c) samt hårde processorkerner og perifere enheder (d). (Billedkilde: Max Maxfield)

Figur 1: De enkleste FPGA'er indeholder kun programmerbar struktur og konfigurerbar IO (GPIO) (a). Forskellige arkitekturer forstærker denne grundlæggende struktur med SRAM-blokke, PLL'er og clock-managers (b), DSP-blokke og SERDES-interfaces (c) samt hårde processorkerner og perifere enheder (d). (Billedkilde: Max Maxfield)

Perifere interfacefunktioner som CAN, I2C, SPI, UART og USB kan implementeres som bløde kerner i den programmerbare struktur, men mange FPGA'er inkluderer dem som hårde kerner i silicium. Tilsvarende kan mikroprocessorer implementeres som bløde kerner i den programmerbare struktur eller som hårde kerner i silicium (figur 1d). FPGA'er med hårde processorkerner kaldes for FPGA'er til System-on-Chip (SoC). Forskellige FPGA'er tilbyder forskellige samlinger af funktioner, egenskaber og kapaciteter målrettet mod forskellige markeder og applikationer.

Der er en række FPGA-leverandører, herunder Altera (som blev erhvervet af Intel), Atmel (som blev erhvervet af Microchip Technology), Efinix, Lattice Semiconductor, Microsemi (som også blev erhvervet af Microchip Technology) og Xilinx.

Alle disse leverandører har flere FPGA-familier. Nogle tilbyder FPGA'er til System-on-Chip (SoC), nogle tilbyder enheder, der er målrettet kunstig intelligens (AI) og maskinlæringsapplikationer (ML), og nogle tilbyder strålingstolerante enheder, der er rettet mod miljøer med høj stråling, for eksempel rummet. Det kan være vanskeligt at vælge den bedste enhed til den aktuelle opgave, fordi der er så mange familier, der hver tilbyder forskellige ressourcer.

Introduktion af Xilinx FPGA'er, SoC'er, MPSoC'er, RFSoC'er og ACAP'er

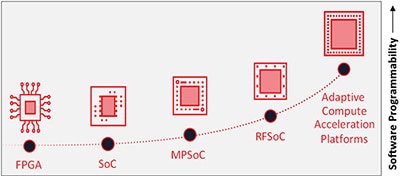

Ydeevnen og funktionaliteten i tilbuddene med programmerbare enheder fra Xilinx spænder over moderat til ekstrem høj. Fra traditionelle FPGA'er, til SoC'er (FPGA-programmerbar struktur med en enkelt processor med hård kerne), MPSoC'er (FPGA-programmerbar struktur med flere processorer med hård kerne), RFSoC'er (MPSoC'er med RF-funktionalitet) og ACAP'er (Adaptive Compute Acceleration Platforms) (figur 2).

Figur 2: Med tiden har Xilinx' arkitekturportefølje udviklet sig fra enkle FPGA'er, der kun indeholdt programmerbar struktur, til SoC-enheder, hvor den programmerbare struktur er styrket med en processor med hård kerne, til MPSoC'er med flere processorer, til RFSoC med RF-funktionalitet, til den seneste generation af ACAP'er, der er målrettet mod applikationer som AI. (Billedkilde: Max Maxfield)

Figur 2: Med tiden har Xilinx' arkitekturportefølje udviklet sig fra enkle FPGA'er, der kun indeholdt programmerbar struktur, til SoC-enheder, hvor den programmerbare struktur er styrket med en processor med hård kerne, til MPSoC'er med flere processorer, til RFSoC med RF-funktionalitet, til den seneste generation af ACAP'er, der er målrettet mod applikationer som AI. (Billedkilde: Max Maxfield)

Xilinx har en så omfattende produktportefølje, henvender sig til så mange markedssegmenter og leverer en så bred vifte af udrulningsmetoder, at det kan være udfordrende for personer, som skal stifte bekendtskab med FPGA'er, at få det store overblik.

For så vidt angår de markeder, som Xilinx henvender sig til, men ikke er begrænset til, datacentre (beregning, netværk, lagring), kommunikation (kabelforbundet, trådløs), luft-/rumfart og forsvar, industri, videnskab og medicin (ISM), test, måling og emulering (TME) samt bilindustri, transmission og forbruger.

For så vidt angår udrulningsmetoder, omfatter de, hvad Xilinx kalder "enheder, der kan tilpasses hardware" (Hardware Adaptable Devices), som omfatter chips, evalueringskort og udviklingskit. Implementerbare slutsystemer, som omfatter SoM'er (system på moduler) og PCIe-acceleratorkort, og FPGA som en tjeneste (FAAS), der omfatter evaluering og udnyttelse af Xilinx-teknologier via førende skytjenesteudbydere, herunder Amazon Web Services (AWS), Alibaba.com og Nimbix.net

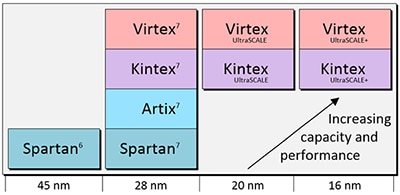

Med hensyn til Xilinx' FPGA-tilbud er én måde at kategorisere disse på efter procesteknologinoden (figur 3).

Figur 3: Xilinx' FPGA-tilbud er en omfattende portefølje med flere noder, der imødekommer behovene over en bred vifte af applikationer. (Billedkilde: Max Maxfield)

Figur 3: Xilinx' FPGA-tilbud er en omfattende portefølje med flere noder, der imødekommer behovene over en bred vifte af applikationer. (Billedkilde: Max Maxfield)

Afhængigt af målapplikationen kan designere vælge en prisbillig FPGA med lille fodaftryk implementeret på en tidligere teknologinode. I tilfælde af en højt avanceret netværksapplikation kan der for eksempel også vælges en højtydende enhed med høj kapacitet og stor båndbredde, der er implementeret på en nyere teknologinode.

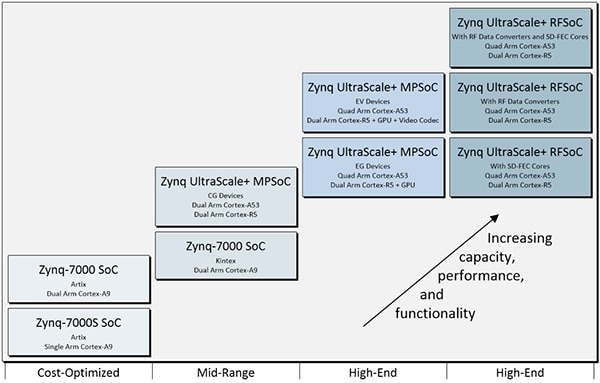

I tilfælde af design, der kræver en eller flere hårde processorkerner (og andre styrkede funktioner som GPU'er, codec'er og SD-FEC-kerner (Soft Decision, Forward Error Correction)), tilbyder Xilinx en portefølje af enheder under paraplynavnet Zynq. En oversigt over tilbud med Zynq SoC, MPSoC og RFSoC er vist på figur 4. Dette udvalg af løsninger giver designere en lang række muligheder for nemmere optimering af effekt, ydeevne, omkostninger og time-to-market.

Figur 4: Xilinx' SoC-, MPSoC- og RFSoC-tilbud integrerer en processors muligheder for softwareprogrammering med en FPGA's muligheder for hardwareprogrammering og giver designere systemydeevne, fleksibilitet og skalerbarhed. (Billedkilde: Max Maxfield)

Figur 4: Xilinx' SoC-, MPSoC- og RFSoC-tilbud integrerer en processors muligheder for softwareprogrammering med en FPGA's muligheder for hardwareprogrammering og giver designere systemydeevne, fleksibilitet og skalerbarhed. (Billedkilde: Max Maxfield)

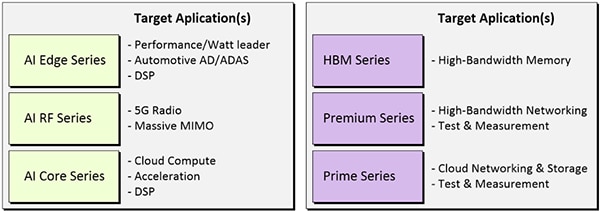

De nyeste tilbud fra Xilinx er Versal ACAP-enheder (Adaptive Compute Acceleration Platform), som alle er implementeret på 7-nanometer (nm) procesteknologinoden. ACAP'er er stærkt integrerede beregningsplatforme med flere kerner, som kan tilpasses forskellige algoritmer samt algoritmer under udvikling. De kan tilpasses dynamisk på hardware- og softwareniveauerne, så de passer til en bred vifte af applikationer og arbejdsbelastninger. Med en arkitektur baseret på en programmerbar NoC (netværk på chip) kan ACAP'er nemt programmeres af både hardwaredesignere og softwareudviklere.

Nye funktioner i Versal-enhederne omfatter intelligente motorer (et massivt array af vektorprocessorer til ML- og DSP-arbejdsbelastninger), en programmerbar NoC med stor båndbredde, lav latens og effekt, der kan flytte terabyte af data, og en integreret skal, der giver bedre ydeevne, udnyttelse og produktivitet med en forhåndsbygget kerneinfrastruktur og systemtilslutning.

En oversigt over Versal ACAP-porteføljen er vist på figur 5.

Figur 5: Xilinx' Versal ACAP'er er stærkt integrerede beregningsplatforme med flere kerner, som kan tilpasses forskellige algoritmer samt algoritmer under udvikling. ACAP'er kan tilpasses dynamisk på hardware- og softwareniveauerne, så de passer til en bred vifte af applikationer og arbejdsbelastninger. (Billedkilde: Max Maxfield)

Figur 5: Xilinx' Versal ACAP'er er stærkt integrerede beregningsplatforme med flere kerner, som kan tilpasses forskellige algoritmer samt algoritmer under udvikling. ACAP'er kan tilpasses dynamisk på hardware- og softwareniveauerne, så de passer til en bred vifte af applikationer og arbejdsbelastninger. (Billedkilde: Max Maxfield)

Som det fremgår af afsnittet om designværktøjer, er en markant forskel knyttet til Versal-enhederne en ny softwarestak, der er målrettet dataeksperter og softwareudviklere samt traditionelle hardwaredesigningeniører.

Der er mange forskellige Xilinx-enheder, der kan fås nu. Nogle få repræsentative tilbud ville være en Artix-7 FPGA, en Kintex UltraScale FPGA, en Kintex UltraScale+ FPGA, et Zynq-7000 SoC Module fra Trenz Electronic GmbH og en Zynq UltraScale+ MPSoC.

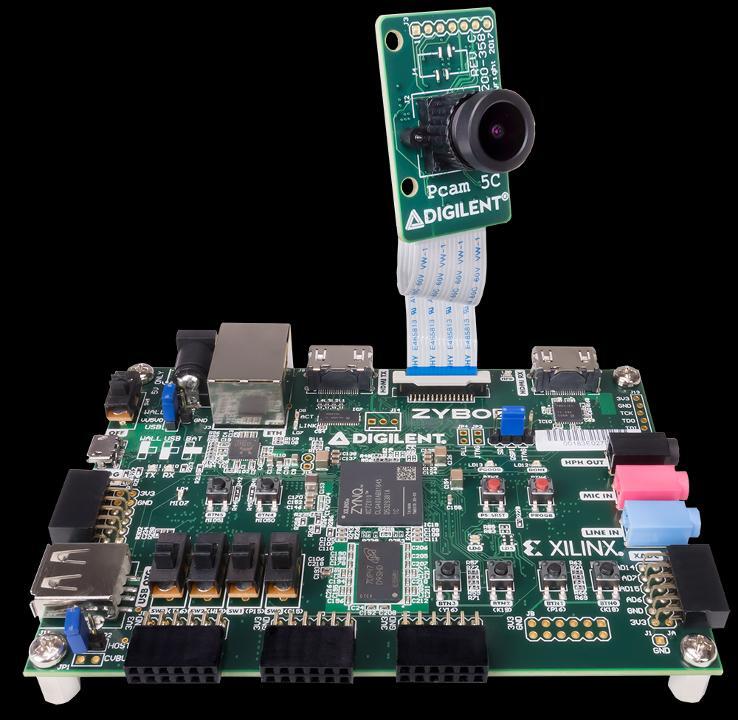

På samme måde er der en lang række tilgængelige evaluerings- og udviklingskort. Nogle repræsentative tilbud ville være et Artix-7 FPGA-evalueringskort fra Digilent, et Kintex UltraScale FPGA-evalueringskort fra Analog Devices, et Kintex UltraScale+ FPGA-evalueringskort fra Xilinx, et Zynq-7000 SoC FPGA-evalueringskort fra Digilent og et Zynq UltraScale+ MPSoC FPGA-evalueringskort også fra Xilinx.

Design og udvikling med Xilinx' FPGA'er, SoC'er og ACAP'er

Ét område, hvor Xilinx virkelig skiller sig ud fra konkurrenterne, er i bredden og dybden af deres designværktøjer og -flows.

I del 1 i denne serie om FPGA'er bemærkede vi, at den traditionelle måde at designe disse enheder på er, at ingeniører bruger et hardwarebeskrivelsessprog (HDL) som Verilog eller VHDL for at indfange designets formål på et abstraktionsniveau kendt som registeroverførselsniveauet (RTL). Disse RTL-beskrivelser kan først simuleres for at bekræfte, at de fungerer efter hensigten, hvorefter de overføres til et synteseværktøj, der genererer den konfigurationsfil, som bruges til at programmere FPGA'en.

Det næste trin op i abstraktion er at indfange designets formål ved hjælp af et programmeringssprog som C/C++, eller en specialimplementering som SystemC, der er et sæt af C++ klasser og makroer, som leverer et hændelsesstyret simuleringsinterface. De muliggør simulering af samtidige processer, der hver især beskrives med almindelig C++ syntaks. Disse beskrivelser kan analyseres og profileres ved at køre dem som almindelige programmer, hvorefter de overføres til en højniveausyntesemotor (HLS), som sender RTL, der lægges ind i den almindelige syntesemotor.

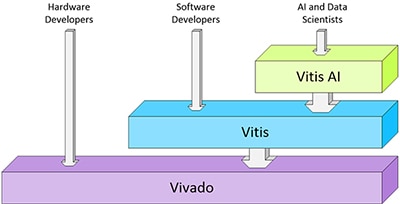

Al denne funktionalitet favnes af Vivado Design Suite HLx Editions, hvis output er den konfigurations-bitstream, som indlæses i de målrettede FPGA-, SoC-, MPSoC-, RFSoC- eller ACAP-enheder. Ud over at gøre det muligt for hardwareudviklere at udnytte C-baseret design og optimeret genbrug leverer Vivado også genbrug af IP-undersystem, automatisering af integration og accelereret "design closure" (figur 6).

Figur 6: En højniveauvisning af Xilinx' Vivado- og Vitis-designværktøjsstak afspejler, hvordan brugere kan arbejde med værktøjerne på de mest hensigtsmæssige abstraktionsniveauer. Hardwaredesignere arbejder med Vivado, softwareudviklere arbejder med Vitis, og AI- og dataeksperter arbejder med Vitis AI. (Billedkilde: Max Maxfield)

Figur 6: En højniveauvisning af Xilinx' Vivado- og Vitis-designværktøjsstak afspejler, hvordan brugere kan arbejde med værktøjerne på de mest hensigtsmæssige abstraktionsniveauer. Hardwaredesignere arbejder med Vivado, softwareudviklere arbejder med Vitis, og AI- og dataeksperter arbejder med Vitis AI. (Billedkilde: Max Maxfield)

Det næste abstraktionsniveau understøttes af Vitis Unified Software Platform, som giver softwareudviklere muligheden for at bygge accelererede applikationer sømløst. Konceptuelt set er Vitis AI "placeret oven på" Vitis, hvilket giver AI- og dataeksperter mulighed for at arbejde på TensorFlow-abstraktionsniveauet. Vitis AI er en udviklingsplatform til AI-inferens på Xilinx' hardwareplatforme, herunder både edge-enheder og Alveo PCIe-kort. Den består af optimeret IP, værktøjer, biblioteker, modeller og designeksempler og er beregnet til at udnytte det fulde potentiale for AI-acceleration på Xilinx' FPGA- og ACAP-enheder.

Vitis AI føres ind i Vitis, som selv føres ind i Vivado. Hovedbudskabet på figur 6 er, at brugere kun "ser", hvad de har brug for at "se". Dvs. hardwareudviklere "ser" kun Vivado, softwareudviklere "ser" kun Vitis, og AI- og dataeksperter "ser" kun Vitis AI. På denne måde kan brugere arbejde med værktøjerne på de mest hensigtsmæssige abstraktionsniveauer.

For softwareudvikleres vedkommende åbner et værktøj som Vitis, der isolerer dem fra den underliggende hardware, FPGA'er op for en langt større gruppe af udviklere. For AI- og dataeksperters vedkommende åbner et værktøj som Vitis AI, der giver dem mulighed for at fokusere på deres eget abstraktionsniveau og isolerer dem fra den underliggende software, på lignende måde FPGA'er op for en ny klasse af udviklere.

Med levering af disse funktionaliteter er Xilinx på forkant med et brancheomfattende fremstød for at bringe FPGA-værktøjer op på endnu højere niveauer af designabstraktion, som vil give udviklere mulighed for nemmere at udnytte funktionaliteten i disse enheder og integrere dem i deres næste design.

Konklusion

Optimale behandlingsdesignløsninger tilvejebringes ofte af kombinationer af processorer og FPGA'er, af FPGA'er alene eller af FPGA'er, der kan opvise hårde processorkerner som en del af deres struktur. Som en teknologi har FPGA'er udviklet sig hurtigt i årenes løb og er i stand til at imødekomme mange designkrav med hensyn til fleksibilitet, behandlingshastighed og effekt, hvilket gør dem yderst nyttige til en lang række applikationer fra intelligente interfaces til maskine-vision og kunstig intelligens.

Som vist spænder tilbuddene med programmerbare enheder fra Xilinx over moderat til ekstrem høj, hvad angår ydeevne og funktionalitet. De dækker lige fra traditionelle FPGA'er, til SoC'er (FPGA-programmerbar struktur med en enkelt processor med hård kerne), MPSoC'er (FPGA-programmerbar struktur med flere processorer med hård kerne), RFSoC'er (MPSoC'er med RF-funktionalitet) og ACAP'er (Adaptive Compute Acceleration Platforms).

Som hjælp til designere med at udvikle design med disse enheder tilbyder Xilinx en række værktøjer til at imødekomme behovene fra hardwareudviklere (Vivado), softwareudviklere (Vitis) samt AI- og dataeksperter (Vitis AI).

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.