Hvorfor og hvordan man bruger Efinix FPGA'er til AI/ML Imaging - Del 1: Kom godt i gang

Bidraget af DigiKey's European Editors

2023-04-20

Redaktørens note: Nye tilgange til FPGA-arkitekturer giver finere kontrol og større fleksibilitet til at imødekomme behovene for maskinindlæring (ML) og kunstig intelligens (AI). Del 1 af denne todelte serie introducerer en sådan arkitektur fra Efinix og hvordan man kommer i gang med det ved hjælp af et udviklingskort. Del 2 diskuterer grænsefladen mellem udviklingskortet og eksterne enheder og periferiudstyr, såsom et kamera.

FPGA'er spiller en kritisk rolle i mange applikationer, fra industriel kontrol og sikkerhed til robotik, luft- og rumfart og bilindustrien. Takket være den fleksible karakter af den programmerbare logik kerne og deres brede grænseflade kapaciteter, en voksende use case for FPGA'er er i billedbehandling, når ML slutning skal implementeres. FPGA'er er ideelle til implementering af løsninger, der har flere højhastighedskameragrænseflader. Desuden gør FPGA'er det også muligt at implementere dedikerede behandlingsrørledninger i logikken og derved fjerne flaskehalse, der ville være forbundet med CPU- eller GPU-baserede løsninger.

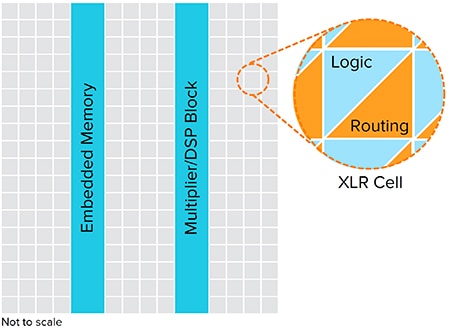

For mange udviklere kræver deres applikationer imidlertid mere ML/AI-funktionalitet og finere kornet kontrol eller routing og logik, ud over hvad klassiske FPGA-arkitekturer med kombinatoriske logiske blokke (CLB'er) kan give. Nyere tilgange til FPGA-arkitekturer behandler disse spørgsmål. Efinix' Quantum-arkitektur bruger f.eks. en XLR-blok (eXchangeable Logic and Routing).

Denne artikel diskuterer nøglefunktioner og attributter i Efinix FPGA-arkitekturen, understreger dens AI/ML-kapaciteter og introducerer implementeringer i den virkelige verden. Det diskuterer derefter et udviklingskort og tilhørende værktøjer, som udviklere kan bruge til hurtigt at komme i gang med deres næste AI/ML-billeddesign.

Efinix FPGA-enheder

Efinix tilbyder i øjeblikket to enhedsintervaller. Virksomheden introducerede oprindeligt Trion-familien, som tilbyder logiske tætheder fra 4000 (4K) til 120K logiske elementer (LE'er), og som fremstilles ved hjælp af en SMIC 40LL-proces. Den nyeste linje af enheder, Titanium-familien, tilbyder logiske tætheder fra 35K til 1 million (1M) logiske elementer og er fremstillet på den meget populære TSMC 16 nanometer (nm) node.

Begge tilbud er baseret på Quantum-arkitekturen, som er unik i FPGA-verdenen. Standard FPGA-arkitekturen er baseret på CLB'er, som på det enkleste niveau indeholder en look-up-tabel (lut) og flip-flops. CLBS implementerer logiske ligninger, der derefter sammenkobles via routing. Efinix' Quantum-arkitektur bevæger sig væk fra forskellige logik- og routing-blokke med XLR-blokken.

Det, der gør en XLR-blok unik, er, at den kan konfigureres til at fungere som en logisk celle med en lut, et register og en adderer eller en routingmatrix. Denne tilgang tilbyder en finkornet arkitektur, der giver rutefleksibilitet, hvilket gør det muligt for implementeringer, der er logisk tunge eller routing tunge for at opnå den ønskede ydeevne.

Figur 1: Det, der gør en XLR-blok unik, er, at den kan konfigureres til at fungere som enten en logisk celle med en lut, et register og en adderer eller en routingmatrix. (Billedkilde: Efinix)

Figur 1: Det, der gør en XLR-blok unik, er, at den kan konfigureres til at fungere som enten en logisk celle med en lut, et register og en adderer eller en routingmatrix. (Billedkilde: Efinix)

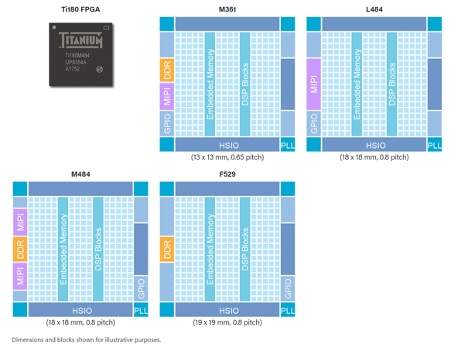

Som den nyeste familie tilbyder Titanium-enhederne de mest avancerede funktioner til udvikleren (figur 2). Sammen med XLR kernen, de giver multi-gigabit serielle links, der opererer på enten 16 gigabit per sekund (Gbps) eller 25,8 Gbps, afhængigt af den valgte enhed. Disse multi-gigabit-forbindelser er afgørende for at muliggøre højhastighedsoverførsel af data på og uden for chippen.

Figur 2: Titanium FPGA Ti180 findes i forskellige muligheder afhængigt af busbredde, I/O og hukommelseskrav. (Billedkilde: Efinix)

Figur 2: Titanium FPGA Ti180 findes i forskellige muligheder afhængigt af busbredde, I/O og hukommelseskrav. (Billedkilde: Efinix)

Titanium-enheder giver også en bred vifte af input/output (I/O )-grænsefladefunktioner, der kan grupperes som generel I/O (GPIO), og som kan understøtte single-ended I/O-standarder som lavspændings CMOS (LVCMOS) ved 3,3 volt, 2,5 volt og 1,8 volt.

Til højhastigheds- og differentialgrænseflade giver Titanium-enhederne højhastigheds-I/O (HSiO), der understøtter single-ended I/O-standarder som LVCMOS ved 1,2 volt, 1,5 volt og SSTL og HSTL. Differential I/O-standarder understøttet af HSIO omfatter lavspændingsdifferentialsignalering (LVDS), differential SSTL og HSTL.

Moderne FPGA'er kræver også tæt forbundet hukommelse med høj båndbredde, som bruges til at gemme billedrammer til billedbehandlingsapplikationer, prøvedata til signalbehandling og selvfølgelig til at køre operativsystemer og software til processorer implementeret inden for FPGA. Titanium-serien af enheder giver mulighed for grænseflade med dynamisk datahastighed fire (DDR4) og DDR4(x) med lavt strømforbrug (LPDDR4(x)). Afhængigt af den valgte Titanium-enhed er busbreddeunderstøttelsen x32 (J) eller x16 (M), mens nogle enheder ikke har LPDDR4-understøttelse (L).

Titanium FPGA'er er SRAM-baserede og kræver en konfigurationshukommelse, hvor enhedskonfigurationen udføres af enten master/slave Serial Peripheral Interconnect (SPI) eller JTAG. For at sikre, at denne konfigurationsmetode er sikker, bruger Titanium FPGA AES GCM-kryptering af bitstrømmen sammen med AES GCM og RSA-4096 til at give bitstream-godkendelse. Stærk sikkerhed som denne er påkrævet, da FPGA'er er indsat på kanten, hvor ondsindede aktører kunne få adgang til og manipulere deres adfærd.

Introduktion til Development Board

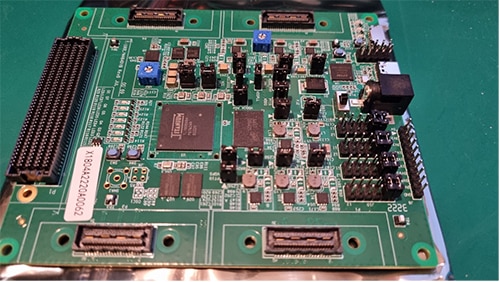

Udviklingskort udgør et kritisk element i FPGA-evalueringsprocessen, da de kan bruges til at udforske mulighederne for en enhed og prototypeapplikationer og derved bidrage til at reducere den samlede risiko. Det første udviklingskort, der er tilgængeligt til at evaluere Titanium FPGA'er og begynde at lave prototyper af applikationer, er Ti180 M484 (Figur 3). Kortet har et FPGA Mezzanine Card (FMC)-stik og fire Samtec QSE-stik.

Figur 3: Sammen med en Titanium FPGA er Ti180 M484-udviklingssættet udstyret med et FMC-stik og fire Samtec QSE-stik. (Billedkilde: Adam Taylor)

Figur 3: Sammen med en Titanium FPGA er Ti180 M484-udviklingssættet udstyret med et FMC-stik og fire Samtec QSE-stik. (Billedkilde: Adam Taylor)

Ti180 FPGA'en, der er monteret på dette udviklingskort, har 172K XLR-celler, 32 globale clocks, 640 DSP-elementer (digital signalbehandling) og 13 megabit (Mbits) indbygget RAM. DSP-elementerne giver mulighed for at implementere 18 x 19 multiplikationer med fast komma og 48-bit multiplikationer. Denne DSP kan også optimeres til SIMD-operationer (single instruction, multiple data), der kører i enten en dual- eller quad-konfiguration. DSP-elementer kan også konfigureres til at udføre floating point-operationer.

Som de fleste udviklingskort har Ti180-udviklingskortet enkle lysdioder og knapper. Dens virkelige styrke ligger dog i dens grænsefladefunktioner. Ti180-udviklingskortet har et FMC-stik med lavt antal pins, som gør det muligt at tilslutte en lang række perifere enheder. Da det er en meget udbredt standard, findes der mange FMC-kort, der muliggør grænseflader til højhastigheds analog-til-digital-konverter (ADC), digital-til-analog-konverter (DAC), netværk og hukommelses-/lagringsløsninger.

Ud over FMC-tilslutningen har kortet fire Samtec QSE-stik, som gør det muligt for udvikleren at tilføje udvidelseskort. Disse QSE-stik bruges til at levere MIPI-ind- og udgange, idet hvert QSE-stik leverer enten en MIPI-ind- eller udgang.

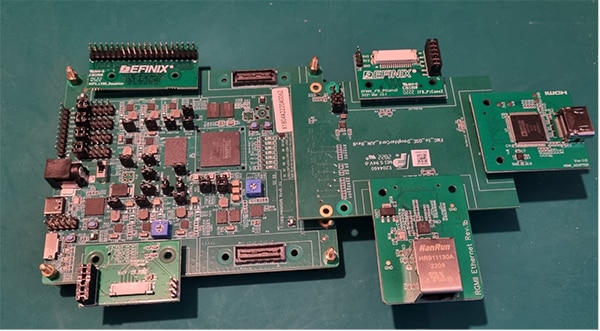

Figur 4: Ti180 M484-udviklingssættet er vist med sit alsidige udvalg af udvidelsesmuligheder baseret på QSE- og FMC-stik. (Billedkilde: Adam Taylor)

Figur 4: Ti180 M484-udviklingssættet er vist med sit alsidige udvalg af udvidelsesmuligheder baseret på QSE- og FMC-stik. (Billedkilde: Adam Taylor)

Ti180-kortet har også 256 Mbits LPDDR4 til understøttelse af den højtydende hukommelse, der kræves i billed- eller signalbehandlingsapplikationer. Desuden tilbyder udviklingskortet en række clockingmuligheder på 25, 33,33, 50 og 74,25 megahertz (MHz), som kan bruges sammen med enhedens PLL (Phase Lock Loop) til at generere forskellige interne frekvenser.

Muligheden for at omprogrammere og debugge live på kortet under udviklingen er afgørende og kræver en JTAG-forbindelse, som er indbygget via et USB-C-interface. Der medfølger også en ikke-flygtig hukommelse i form af to NOR-flash-enheder på 256 MBit, som kan bruges til at demonstrere konfigurationsløsningen.

Kortet får strøm fra en 12-volts universel strømforsyningsadapter, der følger med i æsken. Der medfølger også et FMC-to-QSE break out sammen med QSE-baserede udvidelseskort til HDMI, Ethernet, MIPI og LVDS. For at demonstrere Ti180-billedbehandlingskapaciteterne er der også et dobbelt RPI-datterkort og to IMX477-kamerakort.

Softwaremiljøet

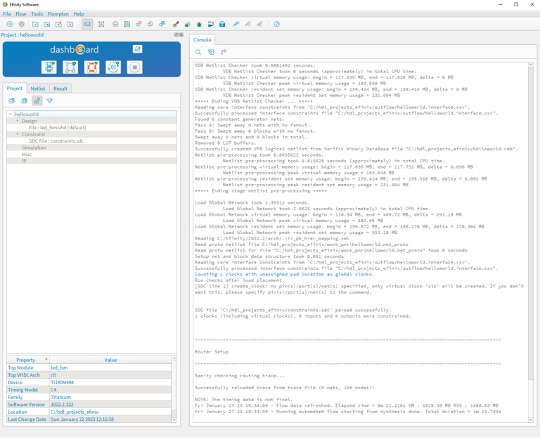

Ved implementering af design, der er rettet mod Ti180-udviklingskortet, anvendes Efinix-softwaren Efinity. Softwaren gør det muligt at generere en bitstrøm via syntese og place and route. Den giver også udviklere intellektuelle ejendomsblokke (IP), timinganalyse og on-chip debugging.

Bemærk, at der kræves et udviklingskort for at få adgang til Efinity-softwaren. I modsætning til andre leverandører har værktøjet dog ikke forskellige versioner, der kræver yderligere licenser.

I Efinity oprettes nye projekter, der er rettet mod den valgte enhed. RTL-filer kan derefter tilføjes til projektet, og der kan oprettes begrænsninger for timing og I/O-design. Det er i Efinity, at udviklere også kan implementere I/O-designet ved hjælp af HSIO, GPIO og specialiserede I/O.

Figur 5: I Efinity oprettes nye projekter, der er rettet mod den valgte enhed. (Billedkilde: Adam Taylor)

Figur 5: I Efinity oprettes nye projekter, der er rettet mod den valgte enhed. (Billedkilde: Adam Taylor)

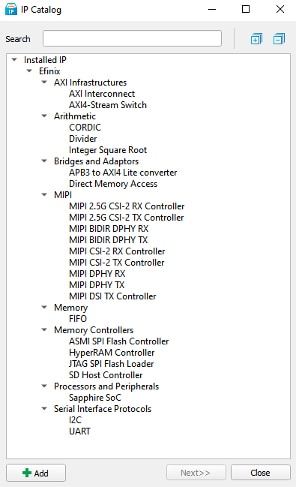

Et kritisk element i FPGA-design er udnyttelse af IP, især for komplekse IP'er som AXI-interconnects, hukommelsescontrollere og softcore-processorer. Efinity giver udviklere en række IP-blokke, der kan bruges til at fremskynde designprocessen.

Figur 6: Efinity giver udviklere et IP-katalog, som de kan bruge til at fremskynde designprocessen. (Billedkilde: Adam Taylor)

Figur 6: Efinity giver udviklere et IP-katalog, som de kan bruge til at fremskynde designprocessen. (Billedkilde: Adam Taylor)

Mens FPGA'er er fremragende til at implementere parallelle behandlingsstrukturer, omfatter mange FPGA-designs softcore-processorer. Disse giver mulighed for at gennemføre sekventiel behandling, f.eks. netværkskommunikation. For at gøre det muligt at implementere softcore-processorerne i Efinix-enhederne leverer Efinity konfigurationsværktøjet Sapphire system-on-chip (SoC). Sapphire giver udvikleren mulighed for at definere et multiprocessorsystem med både caches og cachekohærens på tværs af flere processorer samt mulighed for at køre et indbygget Linux-operativsystem. Inden for Sapphire kan udvikleren vælge mellem en og fire softcore-processorer.

Den softcore-processor, der er implementeret, er VexRiscV soft CPU'en, som er baseret på RISC-V-instruktionssætarkitekturen. VexRiscV-processoren er en 32-bit implementering, som har udvidelser til pipelining og tilbyder et konfigurerbart funktionssæt, hvilket gør den ideel til implementering i Efinix-enheder. Valgfrie konfigurationer omfatter en multiplikator, atomare instruktioner, floating point-udvidelser og komprimerede instruktioner. Afhængigt af SoC-systemets konfiguration vil ydelsen ligge mellem 0,86 og 1,05 DMIPS/MHz.

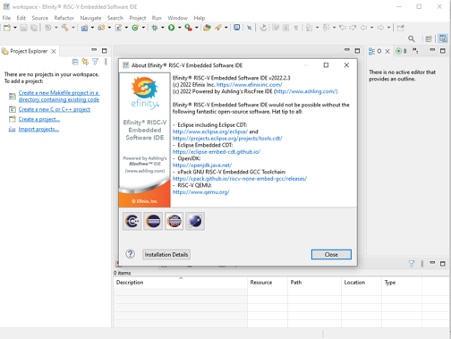

Når hardwaremiljøet er blevet designet og implementeret i Efinix-enheden, kan applikationssoftwaren udvikles ved hjælp af Ashling RiscFree IDE. Ashling RiscFree er en Eclipse-baseret IDE, der gør det muligt at oprette og kompilere applikationssoftware og debugge på målet for at finjustere applikationen før implementering.

Figur 7: Ashling RiscFree er en Eclipse-baseret IDE, der gør det muligt at oprette og kompilere applikationssoftware samt fejlsøge på målet. (Billedkilde: Adam Taylor)

Figur 7: Ashling RiscFree er en Eclipse-baseret IDE, der gør det muligt at oprette og kompilere applikationssoftware samt fejlsøge på målet. (Billedkilde: Adam Taylor)

Hvis der udvikles en indlejret Linux-løsning, leveres alle nødvendige boot-artefakter, herunder First Stage Boot Loader, OpenSBI, U-Boot og Linux ved hjælp af Buildroot. Alternativt kan udvikleren bruge FreeRTOS, hvis der er behov for en realtidsløsning.

Gennemførelse af AI

Efinix' AI-implementering bygger på RISC-V softcore-operationen. Dette udnytter RISC-V-processorens muligheder for brugerdefinerede instruktioner til at accelerere TensorFlow Lite-løsninger. Brugen af RISC-V-processoren gør det også muligt for brugerne at oprette brugerdefinerede instruktioner, der kan bruges som en del af for- eller efterbehandlingen efter AI-inferencen, hvilket skaber en mere responsiv og deterministisk løsning.

For at komme i gang med en AI-implementering er det første skridt at udforske Efinix modelzoo, som er et bibliotek af AI/ML-modeller optimeret til den pågældende slutteknologi. Udviklere, der arbejder med Efinix-enhederne, kan få adgang til modelzooen og træne netværket ved hjælp af Jupyter Notebooks eller Google Colab. Når netværket er blevet trænet, kan det konverteres fra en floating point-model til en kvantiseret model ved hjælp af TensorFlow Lite-konverteren.

Når først TensorFlow Lite-formatet foreligger, kan Efinix' tinyML-accelerator bruges til at skabe en løsning, der kan implementeres på RISC-V-løsningen. tinyML-generatoren gør det muligt for udvikleren at tilpasse acceleratorimplementeringen og generere projektfilerne. Når de anvendes på denne måde, kan accelerationen være mellem 4x og 200x afhængig af den valgte arkitektur og tilpasning.

Konklusion

Efinix-enheder giver udviklere fleksibilitet takket være deres unikke XLR-arkitektur. Værktøjskæden giver mulighed for ikke kun at implementere RTL-design, men også at implementere komplekse SoC-løsninger, der anvender softcore RISC-V-processorer. Oven på softcore SoC'en er der en AI/ML-løsning, som gør det muligt at implementere ML-inferens.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.