Hvorfor og hvordan man bruger Efinix FPGA'er til AI/ML Imaging Del 2: Billedoptagelse og -behandling

Bidraget af DigiKey's European Editors

2023-05-05

Redaktørens note: Nye tilgange til FPGA-arkitekturer giver finere kontrol og større fleksibilitet for at imødekomme behovene for maskinlæring (ML) og kunstig intelligens (AI). Del 1 i denne todelte serie introducerer en sådan arkitektur fra Efinix og viser, hvordan man kommer i gang med den ved hjælp af et udviklingskort. Her diskuteres i del 2, hvordan man forbinder udviklingskortet med eksterne enheder og periferiudstyr som f.eks. et kamera, og hvordan man udnytter FPGA'en til at fjerne flaskehalse i billedbehandlingen.

FPGA'er spiller en afgørende rolle i mange applikationer, lige fra industriel styring og sikkerhed til robotteknologi, rumfart og bilindustrien. Takket være den fleksible karakter af den programmerbare logikkerne og deres brede grænsefladefunktioner er et voksende anvendelsesområde for FPGA'er billedbehandling, hvor der kan anvendes maskinlæring (ML). FPGA'er er ideelle til at implementere løsninger med flere højhastighedskamerainterfaces takket være deres parallelle logikstruktur. Desuden gør FPGA'er det også muligt at bruge en dedikeret behandlingspipeline i logikken og dermed fjerne flaskehalse med delte ressourcer, som ville være forbundet med CPU- eller GPU-baserede løsninger.

Dette andet kig på Efinix' Titanium FPGA'er vil undersøge referenceprogrammet til billedbehandling, der leveres med FPGA'ens Ti180 M484-udviklingskort. Målet er at forstå de enkelte dele af designet og at identificere, hvor FPGA-teknologien gør det muligt at fjerne flaskehalse eller give udviklerne andre fordele.

Det Ti180 M484-baserede referencedesign

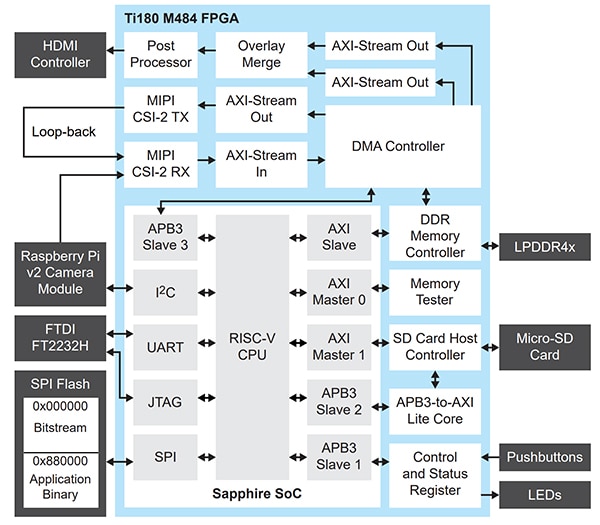

Referencedesignet (figur 1) modtager billeder fra flere MIPI-kameraer (Mobile Industry Processor Interface), udfører frame buffering i LPDDR4x og udsender derefter billederne til en HDMI-skærm (High Definition Multimedia Interface). Et FPGA Mezzanine Card (FMC) og fire Samtec QSE-interfaces på kortet bruges til at levere kameraindgangene og HDMI-udgangen.

Figur 1: Konceptuelt set modtager Ti180 M484-referencedesignet billeder fra flere MIPI-kameraer, udfører frame buffering i LPDDR4x og udsender derefter billederne til en HDMI-skærm. >(Billedkilde: Efinix)

Figur 1: Konceptuelt set modtager Ti180 M484-referencedesignet billeder fra flere MIPI-kameraer, udfører frame buffering i LPDDR4x og udsender derefter billederne til en HDMI-skærm. >(Billedkilde: Efinix)

FMC til QSE-udvidelseskortet bruges sammen med HDMI-datterkortet til at levere udgangsvideovejen, mens tre QSE-stik bruges til at skabe interface med DFRobot SEN0494 MIPI-kameraerne. Hvis der ikke er flere MIPI-kameraer til rådighed, kan et enkelt kamera bruges ved at sløjfe den enkelte kamerakanal tilbage for at simulere yderligere kameraer.

På et overordnet plan kan denne ansøgning synes at være ligetil. Det er imidlertid en udfordring at modtage flere HD-MIPI-strømme (high-definition) med en høj billedhastighed. Det er her, FPGA-teknologien er fordelagtig, fordi den gør det muligt for designere at udnytte flere MIPI-strømme parallelt.

Referencedesignets arkitektur udnytter både parallelle og sekventielle behandlingsstrukturer med FPGA'en. De parallelle strukturer bruges til at implementere billedbehandlingspipelinen, mens en RISC-V processor leverer den sekventielle behandling, der bruges til FPGA-opslagstabellerne (LUT'er).

Billedbehandlingspipelinen kan opdeles i to elementer i mange FPGA-baserede billedbehandlingssystemer, nemlig input- og outputstrømmene. Inputstrømmen forbindes til kamera/sensor-interfacet, og der anvendes behandlingsfunktioner på sensorens output. Disse funktioner kan omfatte Bayer-konvertering, automatisk hvidbalance og andre forbedringer. I outputstrømmen forberedes billedet til visning. Dette omfatter ændring af farverum (f.eks. RGB til YUV) og efterbehandling til det ønskede outputformat, f.eks. HDMI.

Ofte arbejder indgangsbilledbehandlingskæden med sensorens pixelurfrekvens. Dette har en anden timing end outputkæden, som behandles med outputdisplayfrekvensen.

Der bruges en rammebuffer til at forbinde input til outputbehandlingspipeline, som ofte er gemt i ekstern højtydende hukommelse, f.eks. LPDDR4x. Denne rammebuffer afkobles mellem input- og output-pipelines, hvilket giver adgang til rammebufferen via direkte hukommelsesadgang ved den relevante clockfrekvens.

Ti180-referencedesignet anvender en lignende tilgang til de koncepter, der er skitseret ovenfor. Pipelinen til behandling af indgangsbilleder implementerer en intellektuel ejendomskerne (IP) for MIPI Camera Serial Interface 2 (CSI-2) modtageren, som er bygget på det fysiske MIPI-lag (MIPI D-PHY), der kan anvendes til input/output (I/O) i Titanium FPGA'en. MIPI er en udfordrende grænseflade, fordi den bruger både single-ended og differentiel signalering på det samme differentielle par, ud over lavhastighedskommunikation og højhastighedskommunikation. Integrering af MIPI D-PHY i FPGA I/O reducerer kompleksiteten af printkortdesignet og reducerer samtidig materialekortet (BOM).

Når billedstrømmen fra kameraet er modtaget, konverterer referencedesignet derefter output fra MIPI CSI-2 RX til en AXI-strøm (Advanced eXtensible Interface). En AXI Stream er en ensrettet højhastighedsgrænseflade, der leverer en datastrøm fra en master til en slave. Der leveres håndtrykningssignaler til overførsel mellem en master og en slave (tvalid og tready) sammen med sidebåndsignaler. Disse sidebåndssignaler kan bruges til at formidle oplysninger om billedets timing, f.eks. start af billede og slutning af linje.

AXI Stream er ideel til billedbehandlingsapplikationer og gør det muligt for Efinix at levere en række billedbehandlings-IP'er, som derefter nemt kan integreres i behandlingskæden som krævet af applikationen.

Efter modtagelsen konverteres MIPI CSI-2 billeddataene og tidssignalerne til en AXI Stream og indlæses i et DMA-modul (direct memory access), som skriver billedrammen til LPDDR4x og fungerer som rammebuffer.

Dette DMA-modul fungerer under kontrol af RISC-V-kernen i FPGA'en i et Sapphire-system på chip (SoC). Denne SoC giver kontrol, f.eks. ved at stoppe og starte DMA-skrivere, og giver DMA-skrivekanalen de nødvendige oplysninger til korrekt at skrive billeddataene til LPDDR4x. Dette omfatter oplysninger om hukommelsesplaceringen og billedets bredde og højde defineret i bytes.

Udgangskanalen i referencedesignet læser billedoplysningerne fra LPDDR4x-ramebufferen under RISC-V SoC'ens kontrol. Dataene udgives fra DMA-IP'en som en AXI-stream, som derefter konverteres fra RAW-formatet fra sensoren til RGB-format (figur 2) og forberedes til output via den indbyggede Analog Devices' ADV7511 HDMI-sender.

Figur 2: Eksempler på billeder, der udgives fra referencedesignet. (Billedkilde: Adam Taylor)

Figur 2: Eksempler på billeder, der udgives fra referencedesignet. (Billedkilde: Adam Taylor)

Brugen af DMA gør det også muligt for Sapphire SoC RISC-V at få adgang til de billeder, der er gemt i billedbufferen, og til de abstrakte statistikker og billedoplysninger. Sapphire SoC'en er også i stand til at skrive overlays ind i LPDDR4x, så de kan blandes med output-videostrømmen.

Moderne CMOS-billedsensorer (CIS'er) har flere driftstilstande og kan konfigureres til at levere on-chip-behandling og flere forskellige outputformater og clocking-ordninger. Denne konfiguration leveres normalt via en I²C-grænseflade. I Efinix-referencedesignet leveres denne I²C-kommunikation til MIPI-kameraerne af Sapphire SoC RISC-V processoren.

Integration af RISC-V processoren i Titanium FPGA'en reducerer den samlede størrelse af den endelige løsning, da det fjerner behovet for at implementere både komplekse FPGA-tilstandsmaskiner, der øger designrisikoen, og eksterne processorer, der øger BOM'en.

Medtagelsen af processoren muliggør også understøttelse af yderligere IP til at kommunikere med MicroSD-kortet. Dette muliggør anvendelser i den virkelige verden, hvor det kan være nødvendigt at gemme billeder til senere analyse.

Overordnet set er arkitekturen i Ti180-referencedesignet optimeret til at muliggøre en kompakt, billig, men alligevel højtydende løsning, der giver udviklerne mulighed for at reducere BOM-omkostningerne gennem systemintegration.

En af de vigtigste fordele ved referencedesigns er, at de kan bruges til at kickstarte applikationsudvikling på brugerdefineret hardware, så udviklerne kan tage kritiske elementer af designet og bygge videre på det med de tilpasninger, de har brug for. Dette omfatter muligheden for at bruge Efinix' TinyML-flow til at implementere vision-baserede TinyML-applikationer, der kører på FPGA'en. Dette kan udnytte både FPGA-logikkens parallelle karakter og evnen til nemt at tilføje brugerdefinerede instruktioner til RISC-V-processorer, hvilket gør det muligt at skabe acceleratorer inden for FPGA-logikken.

Gennemførelse

Som beskrevet i del 1 er Efinix-arkitekturen unik, fordi den anvender XLR-celler (eXchangeable Logic and Routing) til at levere både routing- og logikfunktionalitet. Et videosystem som referencedesignet er et blandet system, der er både logik- og routingtungt: Der kræves omfattende logik for at implementere billedbehandlingsfunktionerne, og der er behov for omfattende routing for at forbinde IP-cellerne med de nødvendige frekvenser.

Referencedesignet bruger ca. 42 % af XLR-cellerne i enheden, hvilket giver rigelig plads til tilføjelser, herunder brugerdefinerede applikationer som Edge ML.

Brugen af blok-RAM- og DSP-blokke (digital signalbehandling) er også meget effektiv, idet der kun bruges 4 af de 640 DSP-blokke og 40 % af hukommelsesblokkene (figur 3).

|

Figur 3: Ressourceallokering på Efinix-arkitekturen viser, at kun 42 % af XLR-cellerne er brugt, hvilket giver rigelig plads til yderligere processer. (Billedkilde: Adam Taylor)

På enhedens IO bruges DDR-interfacet til LPDDR4x til at levere programhukommelse til Sapphire SoC'en og billedrammebufferne. Alle de enhedsdedikerede MIPI-ressourcer udnyttes sammen med 50 % af faselåsesløjferne (figur 4).

|

Figur 4: Snapshot af grænsefladen og de anvendte I/O-ressourcer. (Billedkilde: Adam Taylor)

GPIO (General Purpose I/O) bruges til at levere I²C-kommunikation sammen med flere af de interfaces, der er forbundet til Sapphire SoC'en, herunder NOR FLASH, USB UART og SD-kort. HSIO bruges til at levere højhastigheds-videooutput til ADC7511 HDMI-senderen.

Et af de afgørende elementer, når man designer med FPGA'er, er ikke kun at implementere og tilpasse designet i FPGA'en, men også at kunne placere logikdesignet i FPGA'en og opnå den krævede timing-ydelse, når det er routed.

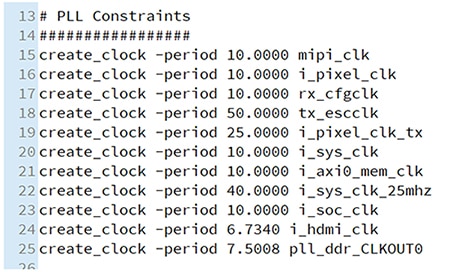

FPGA-designs med et enkelt klokkedomæne er for længst forbi. Der er flere forskellige ure, som alle kører med høje frekvenser i Ti180-referencedesignet. Den endelige timingtabel viser de maksimale frekvenser, der er opnået for systemets ure. Det er her, at den ønskede timingpræstation også kan ses i begrænsningerne (figur 5), som har en maksimal clockfrekvens på 148,5 megahertz (MHz) for HDMI-udgangsklokken.

Figur 5: Urbegrænsninger for referencedesignet. (Billedkilde: Adam Taylor)

Figur 5: Urbegrænsninger for referencedesignet. (Billedkilde: Adam Taylor)

Timingimplementering i forhold til begrænsningerne viser potentialet i Titanium FPGA XLR-strukturen, da den reducerer den mulige routingforsinkelse og dermed øger designets ydeevne (figur 6).

|

Figur 6: Timingimplementering i forhold til begrænsningerne viser potentialet i Titanium FPGA XLR-strukturen til at reducere den mulige routingforsinkelse og dermed øge designets ydeevne. (Billedkilde: Adam Taylor)

Konklusion

Ti180 M484-referencedesignet viser tydeligt mulighederne i Efinix FPGA'er og især Ti180. Designet udnytter flere af de unikke I/O-strukturer til at implementere en kompleks billedbehandlingsvej, der understøtter flere indgående MIPI-strømme. Dette billedbehandlingssystem fungerer under kontrol af en soft-core Sapphire SoC, som implementerer de nødvendige sekventielle behandlingselementer i applikationen.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.