Implementer energibesparende, højtydende edge computing ved hjælp af Efinix' FPGA'er med Quantum-teknologi

Bidraget af DigiKeys nordamerikanske redaktører

2020-03-17

Cloud computing i klassisk forstand er hæmmet af problemer med forsinkelse, datasikkerhed, beskyttelse af slutbrugeres privatliv, disponibel båndbredde og forbindelsens stabilitet. For at overkomme disse problemer går designere og systemarkitekter langsomt over til edge computing. Edge computing medfører dog sine egne udfordringer – fra omkostninger, størrelse, ydeevne og strømforbrug til problemer med skalerbarhed, fleksibilitet og muligheder for opgradering. Det gælder især, når designere ønsker at udføre mere billedbehandling og implementere flere algoritmer til kunstig intelligens (AI) og maskinlæring (ML) tættere på datakilden.

Derfor søger designere nu hinsides traditionelle mikrocontrollere (MCU'er) eller applikationsprocessorer (AP'er), og de overvejer FPGA'er (field-programmable gate arrays) med deres parallelbehandlingsfunktioner. Kontinuerlige forbedringer i designet og implementeringen af FPGA'er betyder, at de nu kan opfylde mange eller alle disse behov – enten som enkeltstående enheder eller sammen med MCU'er og AP'er. Dog er mange designere ikke fortrolige med FPGA'er, og de er bekymrede for læringskurven.

Denne artikel diskuterer kort overgangen fra cloud til edge computing, og hvorfor traditionelle behandlingsarkitekturer kommer til kort over for billedbehandling samt AI og ML. Derefter kaster den et hurtigt blik på FPGA'er, og hvorfor de har en arkitektonisk fordel for disse dataintensive edge-applikationer. Slutteligt introducerer den en ny tilgang til FPGA'er – Efinix' Quantum-teknologi – og hvordan den kan anvendes.

Hvorfor edge computing?

I traditionel cloud computing indsamles data fra en masse forskellige steder, der ligger langt fra hinanden, og disse data sendes til et skybaseret system til opbevaring og analyse. Der er dog mange ulemper ved denne tilgang. De omfatter omkostningerne forbundet med at sende store mængder rå data og bevare integriteten og sikkerheden af dataene undervejs, forsinkelser i respons, bekymringer om slutbrugeres privatliv og ofte upålidelige internetforbindelser samt ineffektiv udnyttelse af båndbredde.

Som navnet antyder, betyder edge computing, at behandlingen – computerberegningerne og analyserne – flyttes tættere på kanten af internettet, dér hvor dataene genereres, analyseres, indsamles og anvendes. Udtrykket edge computing er ikke begrænset til specifikke applikationer eller enheder, og designere kan efter behov vælge "edge-only"-behandling eller en balancegang mellem cloud og edge.

Edge-applikationer omfatter smarte fabrikker, smarte byer, smarte hjem og smart transport for bare at nævne en håndfuld. Edge-enheder kan desuden spænde fra store, high-end edge-servere til relativt små sensorer og aktuatorsystemer på den absolutte yderkant af internettet – dér, hvor dataene genereres.

Fordelen ved FPGA'er

Når det kommer til computerberegninger, er traditionelle processorer ekstremt effektive mht. beslutningstagning og sekventielle opgaver, men forfærdeligt ineffektive mht. mange databehandlingsalgoritmer såsom dem, der bruges til billedbehandling, AI og ML. Disse opgaver kan ofte opdeles i massivt parallelle (versus sekventielle) behandlingspipelines. Faktisk er det netop disse applikationer, der migrerer til kanten og yderkanten.

Det faktum, at FPGA'er kan programmeres (konfigureres) til at implementere en kombination af funktioner, gør det muligt for dem at udføre billedbehandling, AI og ML-algoritmer på en massivt parallel vis og dermed minimere forsinkelsen, samtidig med at strømforbruget reduceres. Ud over deres primære programmerbare struktur er FPGA'er udstyret med DSP-blokke (digital signalbehandling) på chippen – disse indeholder særlige multiplikatorer, som dramatisk accelererer DSP-intensive applikationer. FPGA'er har også integrerede hukommelsesblokke i chippen, og det muliggør behandling på selve chippen, hvilket er meget hurtigere end at skulle gå væk fra chippen.

Der er en række FPGA-leverandører, der hver især har deres egne unikke tilbud. En af leverandørerne, Efinix, har udviklet en særlig FPGA-arkitektur kaldet Quantum, der er unikt egnet til edge computing generelt og til billedbehandling i særdeleshed. Omkring denne teknologi har leverandøren udviklet sin serie af Trion FPGA'er (og Quantum ASIC'er), der giver en firedobbelt forbedring af effekt/ydelse/areal-forholdet sammenlignet med traditionelle FPGA-teknologier (figur 1). Broen mellem FPGA- og ASIC-domænerne er Efinity Integrated Development Environment (IDE).

Figur 1: I kraft af deres fremragende forhold mellem effekt/ydelse/areal er Trion FPGA'er ideelle til applikationer som brugerdefineret logik, beregningsacceleration, maskinlæring, deep learning og billedbehandling. Med Efinity IDE kan brugere nemt migrere fra en Trion FPGA til en Quantum ASIC, der baner vejen for produktion med ultrahøj volumen. (Billedkilde: Efinix)

Figur 1: I kraft af deres fremragende forhold mellem effekt/ydelse/areal er Trion FPGA'er ideelle til applikationer som brugerdefineret logik, beregningsacceleration, maskinlæring, deep learning og billedbehandling. Med Efinity IDE kan brugere nemt migrere fra en Trion FPGA til en Quantum ASIC, der baner vejen for produktion med ultrahøj volumen. (Billedkilde: Efinix)

Hvad er Quantum-teknologi?

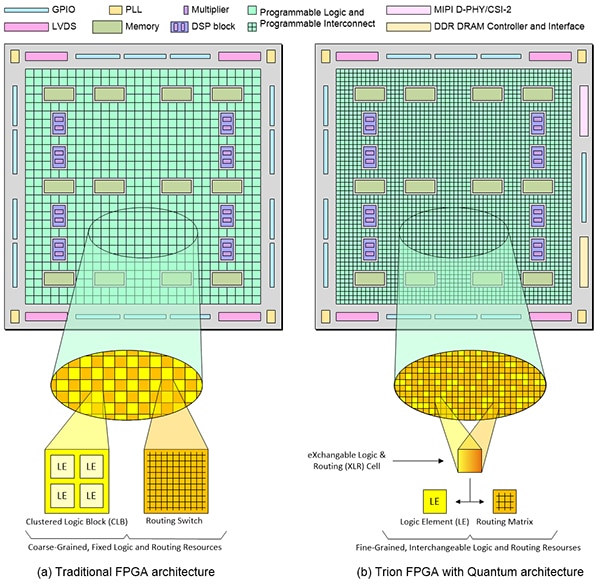

Som traditionelle FPGA'er er Trion FPGA'er udstyret med hukommelse og DSP-blokke. Forskellen ligger i den programmerbare struktur (figur 2). Kernen i programmerbar logik er det logiske element (LE). Hvert LE indeholder en look-up-tabel (LUT), en multiplekser og et register, som alle kan konfigureres efter behov. Traditionelle FPGA'ers programmerbare struktur kan beskrives som "grovkornet".

Figur 2: En traditionel FPGA-arkitektur (a) er grovkornet, og selvom logikken og forbindelsen er programmerbare, er de stadig faste ressourcer. Til sammenligning er Trion FPGA'ers (b) Quantum-arkitektur finkornet, og deres logik- og routingressourcer er indbyrdes udskiftelige (billedkilde: Max Maxfield)

Figur 2: En traditionel FPGA-arkitektur (a) er grovkornet, og selvom logikken og forbindelsen er programmerbare, er de stadig faste ressourcer. Til sammenligning er Trion FPGA'ers (b) Quantum-arkitektur finkornet, og deres logik- og routingressourcer er indbyrdes udskiftelige (billedkilde: Max Maxfield)

I grovkornede strukturer samles flere LE'er i en større, grupperet logikblok (CLB). Bemærk, at nogle leverandører bruger udtrykket konfigurerbar logikblok (CLB), mens andre bruger logik-array-blok (LAB), men de betyder alle det samme.

Det er vigtigt at bemærke, at denne illustration er en abstraktion. CLB'er og routing-kontakter (programmerbar forbindelse) i traditionelle FPGA'er er i virkeligheden ikke opstillet i et skakbrætmønster som vist her. De er dog faste og uforanderlige i den forstand, at programmerbar logik altid vil være programmerbar logik, og programmerbare forbindelser altid vil være programmerbare forbindelser.

Sammenlignet med traditionelle arkitekturer er Trion FPGA'er meget mere finkornede, ned til opløsningen af et enkelt logikelement. Desuden kan hver udskiftelig logik- og routing-celle (XLR) konfigureres til at fungere som en LE eller som en del af routing-matrixen.

De konfigurationsceller, der bruges i Quantum-arkitekturen, er SRAM-baserede, hvilket betyder, at denne teknologi er "silicium-agnostisk". De kan fremstilles via enhver standard CMOS-proces uden behov for særlige behandlingstrin, der kræves med alternative konfigurationsteknologier, som f.eks. flash og antifuse, der bruges i nogle FPGA'er i mellemklassen.

Det er denne softwarekonfigurerbare logik og routing og den højtydende adaptive forbindelse, der giver den Quantum-baserede metode en firdobbelt forbedring af forholdet mellem strøm/ydelse/areal (PPA, power-performance-area) sammenlignet med traditionelle SRAM-baserede FPGA'er, der skabes ved samme procesteknologinode.

FPGA'er, der er skabt ved hjælp af Quantum-arkitekturen, kræver også kun syv metalliseringslag i modsætning til de 12+, der kræves i traditionelle FPGA'er. Da hvert ekstra lag metal fordrer flere maske- og procestrin, er brugen af blot syv lag med til at reducere design- og produktionsomkostningerne og øge udbyttet.

Alle disse egenskaber og funktioner er meget nyttige for designere, der ønsker omkostnings-, størrelses-, ydeevne- og fleksibilitetsmæssige fordele til edge computing og billedbehandling. Trion FPGA'er er derfor velegnede til både traditionelle FPGA-anvendelsesformål og nye edge computing- og billedbehandlingsformål. Sidstnævnte omfatter mobilteknologi, Internet of Things (IoT), automatisering, robotteknologi, sensorfusion, computersyn, AI og ML.

Trion FPGA'ers struktur

Trion FPGA'er er fremstillet vha. en 40 nm (nanometer) lavstrøms-siliciumproces med mellem fire tusinde (K) og 200K LE'er, men processen kan opskaleres til meget større enheder. Alle Trion FPGA'er har hukommelses- og DSP-blokke, men deres kapacitet og antal varierer afhængigt af enhedens størrelse. Mindre enheder såsom T4F81C2 er mere minimalistiske i deres specifikationer (dvs. 3.888 LE'er, 78.848 hukommelsesbits, 59 GPIO'er) og er beregnet til håndholdte kontrolplanfunktioner.

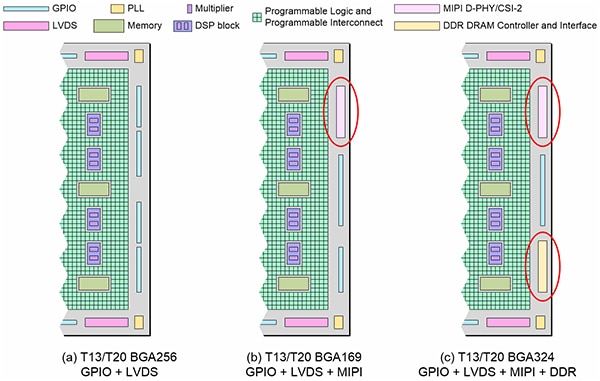

High-end-enheder som T20F256C3 indeholder tilsvarende flere ressourcer (dvs. 19.728 LE'er, 1.069.548 hukommelsesbits, 195 GPIO'er). T13F256C3 svarer til T20F256C3, men har 12.828 LE'er. Desuden findes enheder som T13/T20 i forskellige versioner (figur 3).

Figur 3: Efinix T13/T20 BGA256 (a) er en generisk FPGA, der er et godt valg til design med I/O-intensive behov. T13/T20 BGA169 (b) omfatter to MIPI D-PHY/CSI-2-blokke med hård kerne til design, der skal understøtte MIPI-kameragrænsefladen, og T13/T20 BGA324 (c) udbygger MIPI-grænsefladerne med en x16-bit DDR DRAM-grænseflade og -controller (hård kerne) til design med høje krav til hukommelsesbåndbredden. (Billedkilde: Max Maxfield)

Figur 3: Efinix T13/T20 BGA256 (a) er en generisk FPGA, der er et godt valg til design med I/O-intensive behov. T13/T20 BGA169 (b) omfatter to MIPI D-PHY/CSI-2-blokke med hård kerne til design, der skal understøtte MIPI-kameragrænsefladen, og T13/T20 BGA324 (c) udbygger MIPI-grænsefladerne med en x16-bit DDR DRAM-grænseflade og -controller (hård kerne) til design med høje krav til hukommelsesbåndbredden. (Billedkilde: Max Maxfield)

MIPI CSI-2 er den mest udbredte kameragrænseflade på mobilmarkedet og andre markeder på grund af dens lave strømforbrug, lave forsinkelse og økonomisk fordelagtige forbindelser fra chip til chip. Den understøtter også en bred vifte af højtydende formater, herunder video i 1080p, 4K, 8K og højere, såvel som billeder i høj opløsning. Her er det særligt interessant, at MIPI CSI-2 er den grænseflade, der hyppigst bruges til synssensorer i edge-anvendelsesformål. For at understøtte design til disse anvendelsesformål har T13/T20 BGA169-FPGA'erne to MIPI D-PHY/CSI-2-blokke med hård kerne (også figur 3).

DDR-hukommelse understøtter dataoverførsler med høj båndbredde, men den kræver også overholdelse af en streng timing-protokol. Ud over de hærdede MIPI D-PHY/CSI-2-grænseflader har Trion T13/T20 BGA324 (igen figur 3) også en hærdet x16-bit DDR DRAM-grænseflade og controller til design, hvor der er høje krav til hukommelsesbåndbredden.

Quantum ASIC'er

Som tidligere nævnt er de konfigurationsceller, der bruges i Trion FPGA'er, SRAM-baserede. Som følge heraf skal Trion FPGA'er, når systemet først tændes, have deres konfigurationsdata indlæst, enten fra en ekstern hukommelsesenhed eller ved "bit-banging" via værtsprocessoren. For at kunne gøre dette i produktioner med ultrahøj volumen tilbyder Efinix også Quantum-accelererede integrerede FPGA-løsninger (eFPGA) i form af Quantum ASIC'er. I den forbindelse kan Efinix tage T4-, T8-, T13- eller T20-design og oprette maskeprogrammerede Quantum ASIC-versioner, der starter internt uden behov for en ekstern konfigurationsenhed.

Design og udvikling med Trion FPGA'er

Efinix tilbyder en række evalueringskort og udviklingskit, der giver brugerne mulighed for at blive fortrolige med Trion FPGA'er. Disse omfatter Trion T8F81C-DK T8 Trion FPGA-udviklingskittet, Trion T20F256C-DK T20 Trion FPGA-evalueringskortet, og Trion T20MIPI-DK T20 MIPI D-PHY/CSI-2-udviklingskittet.

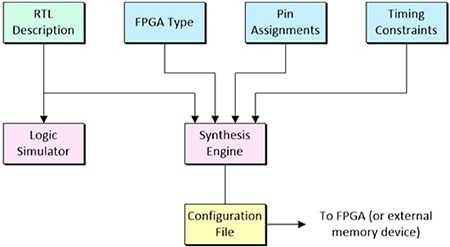

En af de mest almindelige teknikker, der bruges til udvikling med FPGA'er, kaldes sprogdrevet design (LDD). Dette omfatter indfangning af designformålet på et abstraktionsniveau kendt som "Register Transfer Level" (RTL) ved hjælp af et hardwarebeskrivelsessprog (HDL), som f.eks. Verilog eller VHDL. Efter bekræftelse via logiksimulering sendes denne repræsentation til et synteseprogram sammen med yderligere oplysninger som f.eks. FPGA-måltypen, bentildelinger og timingbegrænsninger, såsom maksimal forsinkelse fra input til output. Outputtet fra synteseprogrammet er en konfigurationsfil, som enten indlæses direkte i FPGA'en eller i en ekstern hukommelsesenhed (figur 4).

Figur 4: Efter bekræftelse via logiksimulering sendes RTL-designbeskrivelsen til et synteseprogram sammen med yderligere designdetaljer som FPGA-typen, bentildelinger og timingbegrænsninger. Outputtet fra synteseprogrammet er en konfigurationsfil, som indlæses direkte i FPGA'en. (Billedkilde: Max Maxfield)

Figur 4: Efter bekræftelse via logiksimulering sendes RTL-designbeskrivelsen til et synteseprogram sammen med yderligere designdetaljer som FPGA-typen, bentildelinger og timingbegrænsninger. Outputtet fra synteseprogrammet er en konfigurationsfil, som indlæses direkte i FPGA'en. (Billedkilde: Max Maxfield)

Efinix Efinity IDE falder inden for denne værktøjsklasse. Denne software giver et komplet RTL-til-bitstream-arbejdsforløb med en enkel, brugervenlig grafisk brugergrænseflade (GUI) og understøttelse af kommandolinjescript. Et intuitivt instrumentpanel hjælper udvikleren gennem flowet (dvs. syntese, placering, routing, bitstreamgeneration), hvor hvert trin kan styres automatisk eller manuelt. Udviklere kan bruge Efinitys synteseprogram for at få fuldt udbytte af Quantum-arkitekturen i Trion FPGA'er og skabe enheder med den lovede firdobbelte forbedring af PPA.

Ud over at understøtte simuleringsstrømme via ModelSim, NCSim eller gratis IVerilog-simulatorer har Efinity IDE også en Interface Designer til at begrænse logik og knytte ben til blokke i enhedens periferi, en Floorplan Editor til at gennemgå et designs logik og routing-placering, en Timing Browser og statisk timinganalyse til at måle et designs ydeevne, og en integreret hardware-debugger med logikanalyse og virtuelle I/O-fejlfindingskerner.

Konklusion

Når designere udfører mere billed-, AI- og ML-behandling i kanten i stedet for – eller som supplement til – en skybaseret tilgang, bør de overveje FPGA'er som en del af deres behandlingsarkitektur for at finde bedre løsninger på udfordringer mht. omkostninger, ydeevne, strømforbrug, størrelse, skalerbarhed, fleksibilitet og mulighed for opgradering.

For nogle designere kan dette være forbundet med en vis læringskurve, men som vist kan fremskridt i FPGA'er, som f.eks. Efinix' Quantum-teknologi, hurtigt give afkast af investeringen i form af lavere omkostninger, mindre formfaktorer, højere ydelse og større fleksibilitet.

Som følge heraf er FPGA'er nu ideelt egnet til både traditionelle FPGA-anvendelsesformål og fremspirende edge computing til mobil-, IoT-, automatiserings-, robot-, sensorfusions-, computersyns-, AI- og ML-anvendelsesformål.

Flere ressourcer

- Grundlæggende viden: IoT, IIoT og AIoT – og hvorfor de er fremtiden for industriel automatisering

- Grundlæggende viden om FPGA'er: Hvad er FPGA'er, og hvorfor er de nødvendige?

- Grundlæggende om FPGA'er – del 2: Introduktion til Lattice Semiconductors FPGA'er

- Grundlæggende om FPGA'er – del 3: Introduktion til Microchip Technologys FPGA'er

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.