Brug FPGA hurtig vej til at opbygge højtydende strømeffektive Edge AI-applikationer

Bidraget af DigiKeys nordamerikanske redaktører

2021-01-12

Designere, der ønsker at implementere AI-algoritmer (kunstig intelligens) på inferensprocessorer i udkanten, er under konstant pres for at sænke strømforbruget og udviklingstiden, selv når kravene til behandling øges. Feltprogrammerbare gate-arrays (FPGA'er) tilbyder en særlig effektiv kombination af hastighed og energieffektivitet til implementering af de neurale netværk (NN) inferensmotorer, der kræves til kant AI. For udviklere, der ikke er fortrolige med FPGA'er, kan konventionelle FPGA-udviklingsmetoder imidlertid virke komplekse, hvilket ofte får udviklere til at vende sig til mindre optimale løsninger.

Denne artikel beskriver en enklere tilgang fraMicrochip-teknologi der gør det muligt for udviklere at omgå traditionel FPGA-udvikling for at oprette uddannede NN'er ved hjælp af FPGA'er og et softwareudviklingssæt (SDK) eller bruge et FPGA-baseret videokit til at flytte straks til smart embedded vision applikationsudvikling.

Hvorfor bruge AI ved kanten?

Edge computing giver en række fordele til IoT-applikationer (Internet of Things) i segmenter, der er så forskellige som industriel automatisering, sikkerhedssystemer, smarte hjem og meget mere. I en Industrial IoT-applikation (IIoT), der er målrettet mod fabriksgulvet, kan edge computing dramatisk forbedre responstiden i processtyringssløjfer ved at eliminere forsinkelser i retur til skybaserede applikationer. Tilsvarende kan et kantbaseret sikkerhedssystem eller smart dørlås fortsætte med at fungere, selv når forbindelsen til skyen mistes ved et uheld eller med vilje. I mange tilfælde kan brugen af edge computing i nogen af disse applikationer hjælpe med at sænke de samlede driftsomkostninger ved at reducere produktets afhængighed af skyressourcer. I stedet for at møde et uventet behov for ekstra dyre skyressourcer, efterhånden som efterspørgslen efter deres produkter øges, kan udviklere stole på lokale behandlingsfunktioner, der er indbygget i deres produkter, for at hjælpe med at opretholde mere stabile driftsudgifter.

Den hurtige accept og den øgede efterspørgsel efter maskinlæring (ML) inferensmodeller forstærker dramatisk vigtigheden af edge computing. For udviklere hjælper lokal behandling af inferensmodeller med at reducere responslatens og omkostninger til skyressourcer, der kræves til skybaseret inferens. For brugerne tilføjer brugen af lokale inferensmodeller tillid til, at deres produkter fortsat vil fungere på trods af lejlighedsvis tab af internetforbindelse eller ændringer i produktleverandørens skybaserede tilbud. Derudover kan bekymringer om sikkerhed og privatliv yderligere skabe behovet for lokal behandling og slutning for at begrænse mængden af følsomme oplysninger, der overføres til skyen via det offentlige internet.

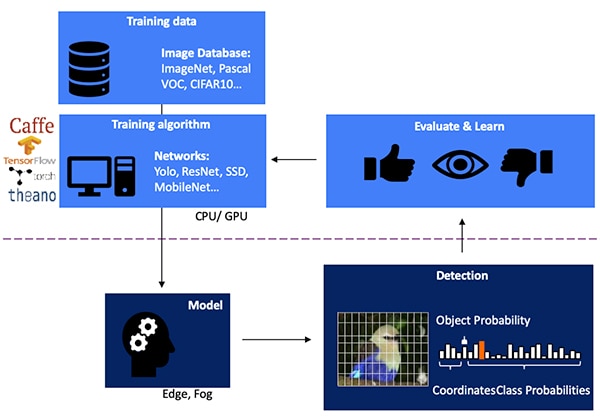

Udvikling af en NN-inferensmodel til visionsbaseret objektdetektion er en flertrinsproces, der starter med modeluddannelse, typisk udført på en ML-ramme såsom TensorFlow ved hjælp af offentligt tilgængelige mærkede billeder eller specialmærkede billeder. På grund af behandlingskravene udføres modeluddannelse typisk med grafikbehandlingsenheder (GPU'er) i skyen eller en anden højtydende computerplatform. Når træningen er afsluttet, konverteres modellen til en inferensmodel, der er i stand til at køre på kant eller tåge-databehandlingsressourcer og levere inferensresultaterne som et sæt sandsynligheder for objektklasse (figur 1).

Figur 1: Implementering af en inferensmodel for kant AI ligger ved afslutningen af en flertrinsproces, der kræver træning og optimering af NN'er på rammer ved hjælp af tilgængelige eller tilpassede træningsdata. (Billedkilde: Microchip Technology)

Figur 1: Implementering af en inferensmodel for kant AI ligger ved afslutningen af en flertrinsproces, der kræver træning og optimering af NN'er på rammer ved hjælp af tilgængelige eller tilpassede træningsdata. (Billedkilde: Microchip Technology)

Hvorfor inferensmodeller er udfordrende beregningsmæssigt

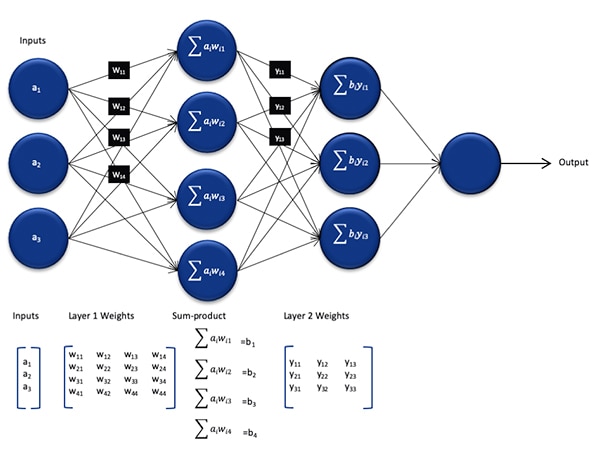

Selvom den er reduceret i størrelse og kompleksitet sammenlignet med den model, der blev brugt under træningsprocessen, præsenterer en NN-inferensmodel stadig en beregningsudfordring for almindelige processorer på grund af det store antal beregninger, det kræver. I sin generiske form omfatter en dyb NN-model flere lag af sæt neuroner. Inden for hvert lag i et fuldt tilsluttet netværk, hver neuron nij skal beregne summen af produkter fra hver input med en tilhørende vægt wij (Figur 2).

Figur 2: Antallet af beregninger, der kræves for inferens med et NN, kan pålægge en betydelig beregningsmæssig arbejdsbyrde. (Billedkilde: Microchip Technology)

Figur 2: Antallet af beregninger, der kræves for inferens med et NN, kan pålægge en betydelig beregningsmæssig arbejdsbyrde. (Billedkilde: Microchip Technology)

Ikke vist i figur 2 er det yderligere beregningskrav, der stilles af aktiveringsfunktionen, der ændrer output fra hver neuron ved at kortlægge negative værdier til nul, kortlægningsværdier større end 1 til 1 og lignende funktioner. Outputtet af aktiveringsfunktionen for hver neuron nij fungerer som input til det næste lag i + 1 og fortsætter på denne måde for hvert lag. Endelig producerer outputlaget i NN-modellen en outputvektor, der repræsenterer sandsynligheden for, at den originale inputvektor (eller matrix) svarer til en af de klasser (eller etiketter), der anvendes under den overvågede læringsproces.

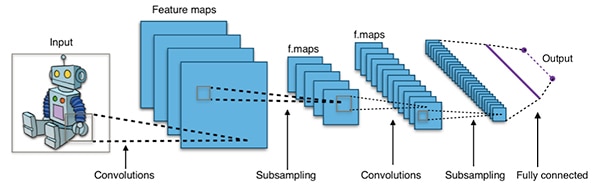

Effektive NN-modeller er bygget med arkitekturer, der er meget større og mere komplekse end den repræsentative generiske NN-arkitektur, der er vist ovenfor. For eksempel anvender et typisk foldnings-NN (CNN), der anvendes til detektering af billedobjekter, disse principper på en stykkevis måde, og scanner på tværs af bredden, højden og farvedybden af et inputbillede for at producere en række funktionskort, der endelig giver outputforudsigelsesvektoren (Figur 3).

Figur 3: CNN'er, der anvendes til detektering af billedobjekter, involverer et stort antal neuroner i mange lag, hvilket pålægger større efterspørgsel på beregningsplatformen. (Billedkilde: Aphex34 CC BY-SA 4.0)

Figur 3: CNN'er, der anvendes til detektering af billedobjekter, involverer et stort antal neuroner i mange lag, hvilket pålægger større efterspørgsel på beregningsplatformen. (Billedkilde: Aphex34 CC BY-SA 4.0)

Brug af FPGA'er til at fremskynde NN-matematik

Selvom der fortsat dukker en række muligheder op til udførelse af inferensmodeller ved kanten, er der få alternativer, der giver en optimal blanding af fleksibilitet, ydeevne og effektivitet, der er nødvendig for praktisk højhastighedsinferens ved kanten. Blandt let tilgængelige alternativer til kant AI er FPGA'er særligt effektive, fordi de kan levere højtydende hardwarebaseret udførelse af computerintensive operationer, mens de bruger relativt lidt strøm.

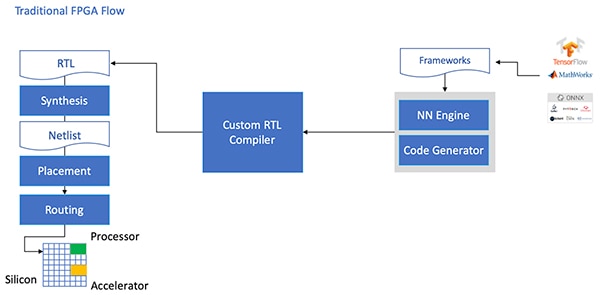

På trods af deres fordele bliver FPGA'er undertiden omgået på grund af et traditionelt udviklingsflow, der kan være skræmmende for udviklere uden omfattende FPGA-erfaring. For at skabe en effektiv FPGA-implementering af en NN-model genereret af en NN-ramme, skal udvikleren forstå nuancerne ved at konvertere modellen til registeroverførselssprog (RTL), syntetisere designet og arbejde gennem det endelige sted og rute fysisk design fase for at producere en optimeret implementering (figur 4).

Figur 4: For at implementere en NN-model på en FPGA har udviklere indtil nu haft brug for at forstå, hvordan de konverterer deres modeller til RTL og arbejder gennem det traditionelle FPGA-flow. (Billedkilde: Microchip Technology)

Figur 4: For at implementere en NN-model på en FPGA har udviklere indtil nu haft brug for at forstå, hvordan de konverterer deres modeller til RTL og arbejder gennem det traditionelle FPGA-flow. (Billedkilde: Microchip Technology)

Med sinPolarFire FPGA'er, specialsoftware og tilhørende intellektuel ejendomsret (IP), Microchip Technology giver en løsning, der gør højtydende inferens med lav effekt ved kanten bredt tilgængelig for udviklere uden FPGA-erfaring.

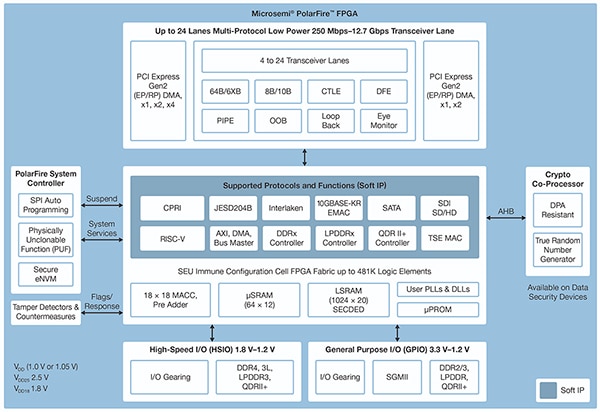

PolarFire FPGA'erne er fremstillet i en avanceret ikke-flygtig procesteknologi og er designet til at maksimere fleksibilitet og ydeevne og samtidig minimere strømforbruget. Sammen med et omfattende udvalg af højhastighedsgrænseflader til kommunikation og input / output (I / O) har de et dybt FPGA-stof, der understøtter avanceret funktionalitet ved hjælp af bløde IP-kerner, herunder RISC-V-processorer, avancerede hukommelsescontrollere og andre standardgrænsefladesubsystemer (figur 5).

Figur 5: Microchip Technology PolarFire-arkitekturen giver et dybt stof designet til at understøtte højtydende designkrav inklusive beregningskrævende implementering af inferensmodeller. (Billedkilde: Microchip Technology)

Figur 5: Microchip Technology PolarFire-arkitekturen giver et dybt stof designet til at understøtte højtydende designkrav inklusive beregningskrævende implementering af inferensmodeller. (Billedkilde: Microchip Technology)

PolarFire FPGA-stoffet giver et omfattende sæt logiske elementer og specialblokke, der understøttes i en række kapaciteter af forskellige medlemmer af PolarFire FPGA-familien, inklusiveMPF100T ,MPF200T ,MPF300T ogMPF500T serie (tabel 1).

|

Tabel 1: En række FPGA-stoffunktioner og kapaciteter er tilgængelige i PolarFire-serien. (Tabelkilde: DigiKey, baseret på Microchip Technology PolarFire datablad)

Blandt funktionerne af særlig interesse for inferensacceleration inkluderer PolarFire-arkitekturen en dedikeret matematikblok, der giver en 18-bit × 18-bit signeret multiply-accumulate-funktion (MAC) med en pre-adder. En indbygget dot-produkttilstand bruger en enkelt matematisk blok til at udføre to 8-bit multipliceringsoperationer, hvilket giver en mekanisme til at øge kapaciteten ved at udnytte den ubetydelige indvirkning af modelkvantisering på nøjagtigheden.

Ud over at fremskynde de matematiske operationer hjælper PolarFire-arkitekturen med at lindre den slags hukommelsesproblemer, der opstår, når der implementeres inferensmodeller på arkitekturer til generelle formål, såsom små distribuerede hukommelser til lagring af mellemresultater oprettet under NN-algoritmeudførelse. En NN-modellens vægte og forspændingsværdier kan også lagres i en 16 dyb med 18-bit koefficient, skrivebeskyttet hukommelse (ROM) bygget fra logiske elementer placeret nær matematikblokken.

Kombineret med andre PolarFire FPGA-stoffunktioner giver matematiske blokke grundlaget for Microchip Technology's CoreVectorBlox IP på højere niveau. Dette fungerer som en fleksibel NN-motor, der er i stand til at udføre forskellige typer NN'er. Sammen med et sæt kontrolregistre indeholder CoreVectorBlox IP tre vigtige funktionelle blokke:

- Microcontroller: En simpel RISC-V soft processor, der læser Microchip firmware binært stort objekt (BLOB) og brugerens specifikke NN BLOB-fil fra eksternt lager. Det styrer de overordnede CoreVectorBlox-operationer ved at udføre instruktioner fra firmwarebloben.

- Matrix-processor (MXP): En blød processor, der består af otte 32-bit aritmetiske logiske enheder (ALU'er) og designet til at udføre parallelle operationer på datavektorer ved hjælp af elementvis tensoroperationer, herunder add, sub, xor, shift, mul, dotprod og andre, ved hjælp af blandet 8-bit, 16-bit og 32-bit præcision efter behov.

- CNN-accelerator: Accelererer MXP-operationer ved hjælp af et todimensionalt array af MAC-funktioner implementeret ved hjælp af matematiske blokke og drift med 8-bit præcision.

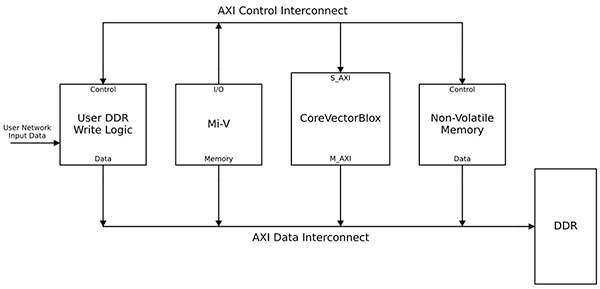

Et komplet NN-behandlingssystem vil kombinere en CoreVectorBlox IP-blok, hukommelse, hukommelsescontroller og en værtsprocessor, såsom Microsoft RISC-V (Mi-V) softwareprocessorkerne (figur 6).

Figur 6: CoreVectorBlox IP-blokken fungerer med en værtsprocessor som Microchips Mi-V RISC-V-mikrocontroller til implementering af en NN-inferensmodel. (Billedkilde: Microchip Technology)

Figur 6: CoreVectorBlox IP-blokken fungerer med en værtsprocessor som Microchips Mi-V RISC-V-mikrocontroller til implementering af en NN-inferensmodel. (Billedkilde: Microchip Technology)

I en videosystemimplementering ville værtsprocessoren indlæse firmware- og netværksBLOB'erne fra systemflashukommelsen og kopiere dem til dobbelt datahastighed (DDR) random access memory (RAM) til brug af CoreVectorBlox-blokken. Når videorammer ankommer, skriver værtsprocessoren dem i DDR RAM og signaliserer CoreVectorBlox-blokken for at begynde at behandle billedet. Efter at den har kørt den inferensmodel, der er defineret i netværket BLOB, skriver CoreVectorBlox-blokken resultaterne, inklusive billedklassifikation, tilbage i DDR RAM til brug af målapplikationen.

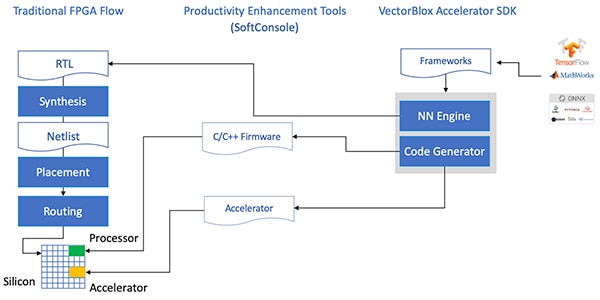

Udviklingsflow forenkler NN FPGA-implementering

Mikrochip beskytter udviklere mod kompleksiteten ved at implementere en NN-inferensmodel på PolarFire FPGA'er. I stedet for at håndtere detaljerne i den traditionelle FPGA-strøm arbejder NN-modeludviklere som normalt med deres NN-rammer og indlæser den resulterende model i Microchip Technology'sVectorBlox Accelerator Softwareudviklingssæt (SDK). SDK genererer det krævede sæt filer inklusive dem, der er nødvendige for den normale FPGA-udviklingsflow og de tidligere nævnte firmware- og netværksBLOB-filer (figur 7).

Figur 7: VectorBlox Accelerator SDK administrerer detaljerne i implementering af en NN-model på en FPGA og genererer automatisk filer, der er nødvendige for at designe og køre den FPGA-baserede inferensmodel. (Billedkilde: Microchip Technology)

Figur 7: VectorBlox Accelerator SDK administrerer detaljerne i implementering af en NN-model på en FPGA og genererer automatisk filer, der er nødvendige for at designe og køre den FPGA-baserede inferensmodel. (Billedkilde: Microchip Technology)

Fordi VectorBlox Accelerator SDK-strømmen lægger NN-designet på NN-motoren, der er implementeret i FPGA, kan forskellige NN'er køre på det samme FPGA-design uden behov for at gentage FPGA-designsyntesestrømmen. Udviklere opretter C / C ++ - kode til det resulterende system og er i stand til at skifte modeller inden for systemet i farten eller køre modeller samtidigt ved hjælp af tidsskæring.

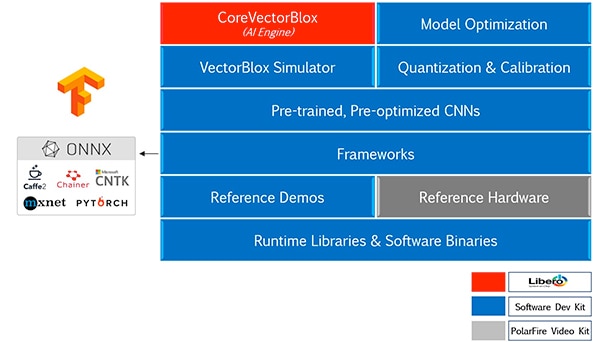

VectorBlox Accelerator SDK smelter Microchip-teknologienLibero FPGA-designsuite med et omfattende sæt funktioner til udvikling af NN-inferensmodel. Sammen med modeloptimering, kvantisering og kalibreringstjenester tilbyder SDK en NN-simulator, der lader udviklere bruge de samme BLOB-filer til at evaluere deres model inden deres anvendelse i FPGA-hardwareimplementeringen (figur 8).

Figur 8: VectorBlox Accelerator SDK leverer et omfattende sæt tjenester designet til at optimere FPGA-implementering af rammegenererede inferensmodeller. (Billedkilde: Microchip Technology)

Figur 8: VectorBlox Accelerator SDK leverer et omfattende sæt tjenester designet til at optimere FPGA-implementering af rammegenererede inferensmodeller. (Billedkilde: Microchip Technology)

VectorBlox Accelerator SDK understøtter modeller i Open Neural Network Exchange (ONNX) -format samt modeller fra en række rammer, herunder TensorFlow, Caffe, Chainer, PyTorch og MXNET. Understøttede CNN-arkitekturer inkluderer MNIST, MobileNet-versioner, ResNet-50, Tiny Yolo V2 og Tiny Yolo V3. Microchip arbejder på at udvide support til at omfatte de fleste netværk i open sourceOpenVINO værktøjssætåben model zoo af foruddannede modeller, herunder Yolo V3, Yolo V4, RetinaNet og SSD-MobileNet, blandt mange andre.

Video-kit demonstrerer FPGA-slutning

For at hjælpe udviklere med at komme hurtigt ind i smart embedded vision-applikationsudvikling, tilbyder Microchip Technology en omfattende prøveapplikation designet til at køre på virksomhedensMPF300-VIDEO-KIT PolarFire FPGA Video and Imaging Kit og reference design.

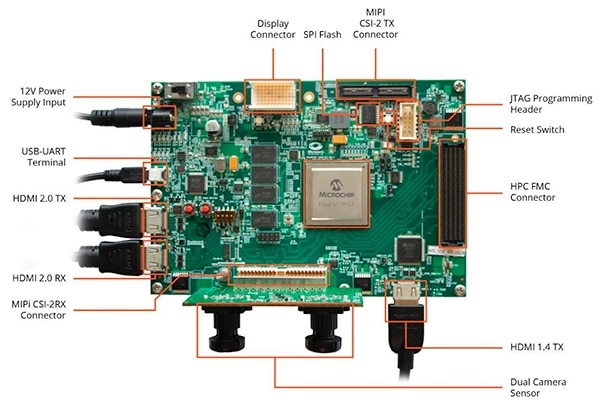

Baseret på Microchip MPF300T PolarFire FPGA kombinerer sættets kort en dobbelt kamerasensor, dobbelt datahastighed 4 (DDR4) RAM, flash-hukommelse, strømstyring og en række grænseflader (figur 9).

Figur 9: MPF300-VIDEO-KIT PolarFire FPGA Video and Imaging Kit og tilhørende software giver udviklere en hurtig start til FPGA-baseret inferens i smarte indlejrede visionapplikationer. (Billedkilde: Microchip Technology)

Figur 9: MPF300-VIDEO-KIT PolarFire FPGA Video and Imaging Kit og tilhørende software giver udviklere en hurtig start til FPGA-baseret inferens i smarte indlejrede visionapplikationer. (Billedkilde: Microchip Technology)

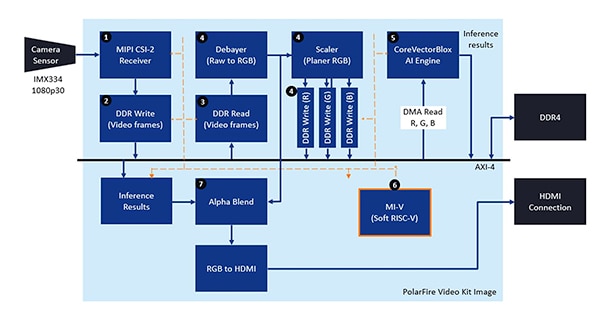

Sættet leveres med et komplet Libero-designprojekt, der bruges til at generere firmware og BLOB-filer i netværket. Efter programmering af BLOB-filerne i den indbyggede flashhukommelse skal udviklerne klikke på køreknappen i Libero for at starte demonstrationen, som behandler videobilleder fra kamerasensoren og viser inferensresultater på et display (figur 10).

Figur 10: Microchip Technology PolarFire FPGA Video and Imaging Kit demonstrerer, hvordan man designer og bruger en FPGA-implementering af et smart integreret vision-system, der er bygget op omkring Microchip CoreVectorBlox NN-motoren. (Billedkilde: Microchip Technology)

Figur 10: Microchip Technology PolarFire FPGA Video and Imaging Kit demonstrerer, hvordan man designer og bruger en FPGA-implementering af et smart integreret vision-system, der er bygget op omkring Microchip CoreVectorBlox NN-motoren. (Billedkilde: Microchip Technology)

For hver input-videoramme udfører det FPGA-baserede system følgende trin (med trinnumre, der korrelerer med figur 10):

- Læg en ramme fra kameraet

- Gem rammen i RAM

- Læs rammen fra RAM

- Konverter det rå billede til RGB, planer RGB, og gem resultatet i RAM

- Mi-V soft RISC-V-processor starter CoreVectorBlox-motoren, som henter billedet fra RAM, udfører inferens og gemmer klassificeringssandsynlighedsresultaterne tilbage til RAM

- Mi-V bruger resultaterne til at oprette en overlay-ramme med afgrænsningsfelter, klassificeringsresultater og andre metadata og gemmer rammen i RAM

- Den originale ramme blandes med overlayrammen og skrives til HDMI-skærmen

Demonstrationen understøtter acceleration af Tiny Yolo V3 og MobileNet V2-modeller, men udviklere kan køre andre SDK-understøttede modeller ved hjælp af de metoder, der er beskrevet tidligere ved at foretage en lille kodeændring for at tilføje modelnavnet og metadata til den eksisterende liste, der indeholder de to standardmodeller.

Konklusion

AI-algoritmer, såsom NN-modeller, pålægger typisk beregningskrævende arbejdsbelastninger, der kræver mere robuste computerressourcer end tilgængelige med almindelige processorer. Mens FPGA'er er veludstyrede til at imødekomme ydeevnen og lave strømkrav ved udførelse af inferensmodeller, kan konventionelle FPGA-udviklingsmetoder virke komplekse, hvilket ofte får udviklere til at henvende sig til suboptimale løsninger.

Som vist ved hjælp af specialiseret IP og software fra Microchip Technology, kan udviklere uden FPGA-erfaring implementere inferensbaserede design, der bedre er i stand til at opfylde krav til ydelse, strøm samt designplan.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.