Sådan bruges FPGA SoC'er til sikre og tilsluttede hårde realtidssystemer

Bidraget af DigiKeys nordamerikanske redaktører

2023-02-16

FPGA'er (Field programmable gate arrays), Linux-egnede RISC-V-mikrocontrollerunits (MCU'er), avancerede hukommelsesarkitekturer og højtydende kommunikationsinterfaces er vigtige værktøjer for designere. Dette gælder især for designere af sikre tilsluttede systemer, sikkerhedskritiske systemer og en lang række deterministiske systemer med hård realtid som f.eks. kunstig intelligens (AI) og maskinlæring (ML).

Integrationen af disse forskellige elementer i et sikkert, forbundet og deterministisk system kan imidlertid være en udfordrende og tidskrævende aktivitet, ligesom det kan være vanskeligt at etablere højhastighedsforbindelser til de forskellige systemelementer. Designere skal medtage en enhed til hukommelsesstyring, en enhed til hukommelsesbeskyttelse, sikker opstartskapacitet og gigabit-transceivere til højhastighedsforbindelser. Designet vil kræve aktiv og statisk strømstyring og styring af indløbsstrømme. Nogle konstruktioner vil kræve drift i det udvidede kommercielle temperaturområde på 0 °C til +100 °C junction temperature (TJ), mens systemer i industrielle miljøer vil skulle fungere ved TJ fra -40 °C til +100 °C.

For at imødegå disse og andre udfordringer kan designere henvende sig til FPGA-system-on-chip (SoC)-enheder, der kombinerer lavt strømforbrug, termisk effektivitet og sikkerhed i forsvarskvalitet til intelligente, forbundne og deterministiske systemer.

I denne artikel gennemgår vi arkitekturen af en sådan FPGA SoC, og hvordan den understøtter effektivt design af forbundne og deterministiske systemer. Derefter præsenteres kort EEMBC CoreMark-Pro-benchmark for processorkraft i forhold til strømforbrug sammen med en oversigt over benchmarkpræstationen for en repræsentativ FPGA SoC. Den ser på, hvordan sikkerhed er indbygget i disse FPGA SoC'er, og beskriver eksemplariske FPGA SoC'er fra Microchip Technology sammen med en udviklingsplatform til at fremskynde designprocessen. Den afsluttes med en kort liste over udvidelseskort fra MikroElektronika, der kan bruges til at implementere en række kommunikationsinterfaces samt GNSS-placeringsmuligheder (Global Navigation Satellite System).

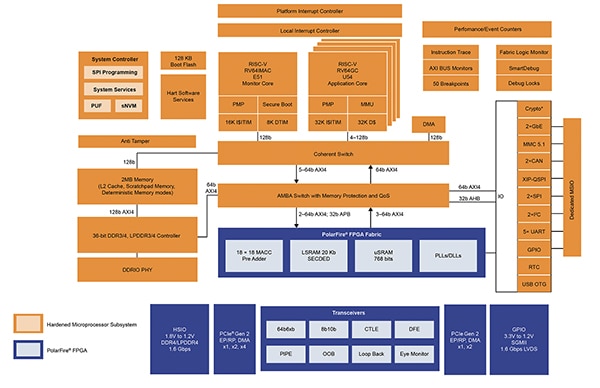

SoC'er bygget med FPGA-strukturen

"Chippen" for denne SoC er en FPGA-struktur, der indeholder systemelementerne, fra FPGA'en til RISC-V MCU-subsystemet, der er bygget med hærdet FPGA-logik. MCU-undersystemet omfatter en quad-core RISC-V MCU-klynge, en RISC-V-monitorkerne, en systemcontroller og et deterministisk Level 2- (L2-) hukommelsesundersystem. FPGA'en i disse SoC'er indeholder op til 460 K logikelementer, op til 12,7 gigabit per sekund (Gbps) transceivers og andre input/output (I/O) blokke, herunder generel I/O (GPIO) og Peripheral Component Interconnect Express (PCIe) 2. Den overordnede arkitektur er designet med henblik på pålidelighed. Den omfatter enkeltfejlkorrektion og dobbeltfejlsdetektion (SECDED) på alle hukommelser, differentiel effektanalyse (DPA), fysisk hukommelsesbeskyttelse og 128 kilobits (Kbits) flash-opstarthukommelse (figur 1).

Figur 1: Alle elementer i denne FPGA SoC, herunder RISC-V-subsystemerne, er implementeret på FPGA-strukturen. (Billedkilde: Microchip Technology)

Figur 1: Alle elementer i denne FPGA SoC, herunder RISC-V-subsystemerne, er implementeret på FPGA-strukturen. (Billedkilde: Microchip Technology)

Microchip tilbyder sit Mi-V-økosystem (udtales "my five") af tredjepartsværktøjer og designressourcer til støtte for implementeringen af RISC-V-systemer. Den er bygget til at fremskynde indførelsen af RISC-V instruktionssæt arkitekturen (ISA) for hærdede RISC-V kerner og for RISC-V soft cores. Elementer i Mi-V-økosystemet omfatter adgang til:

- Licenser vedrørende intellektuel ejendomsret (IP)

- Hardware

- Operativsystemer og middleware

- Debuggere, compilere og designtjenester

De hærdede RISC-V MCU'er i FPGA SoC'en omfatter adskillige debuggingfunktioner som passivt konfigurerbar AXI-interface (advanced extensible interface) og instruktionssporing. AXI gør det muligt for designere at overvåge data, der skrives til eller læses fra forskellige hukommelser, og at vide, hvornår de bliver skrevet eller læst.

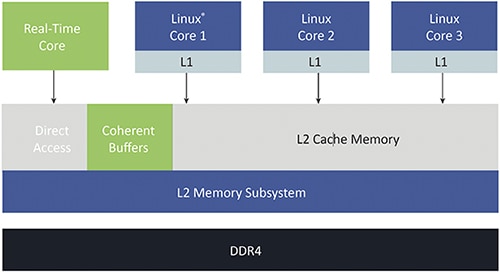

RISC-V MCU-undersystemet anvender en femtrins pipeline i fem trin med en enkelt trin-impuls, i rækkefølge. Den er ikke sårbar over for Spectre- eller Meltdown-eksplosioner, som kan ramme out-of-order-arkitekturer. Alle fem MCU'er er sammenhængende med hukommelses subsystemet og understøtter en blanding af deterministiske asymmetriske multiprocessingssystemer (AMP) i realtidsmodus og Linux. RISC-V-delsystemet har bl.a. følgende muligheder (figur 2):

- Kør Linux og hårde realtidsoperationer

- Konfigurer L1 og L2 som deterministisk hukommelse

- DDR4-hukommelsesundersystem

- Deaktivere/aktivere grenprædiktorer

- Drift af rørledning i ordre

Figur 2: RISC-V-undersystemet omfatter flere processor- og hukommelseselementer. (Billedkilde: Microchip Technology)

Figur 2: RISC-V-undersystemet omfatter flere processor- og hukommelseselementer. (Billedkilde: Microchip Technology)

Mere forarbejdning med mindre energi

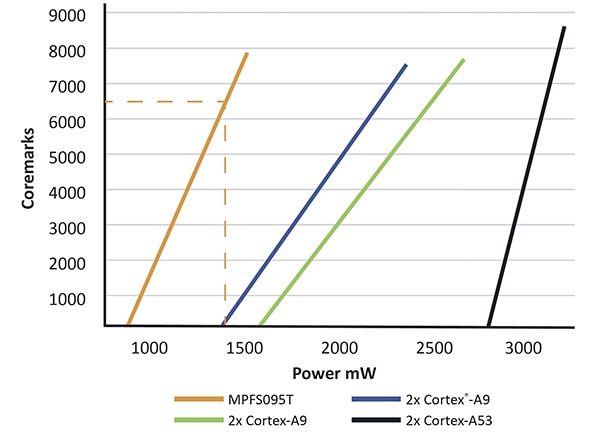

Ud over deres fordele ved systemdrift, herunder understøttelse af hård realtidsbehandling, er disse FPGA SoC'er meget energieffektive. EEMBC CoreMark-PRO benchmark er en industristandard for sammenligning af MCU'ernes effektivitet og ydeevne i indlejrede systemer. Den er udviklet specielt til at benchmarke hardwarens ydeevne og erstatte Dhrystone-benchmarket.

CoreMark-PRO-arbejdsbelastningerne omfatter en bred vifte af ydelseskarakteristika, parallelitet på instruktionsniveau og hukommelsesudnyttelse baseret på fire arbejdsbelastninger med flydende komma og fem almindelige hele talbelastninger. Fedtpunktsbelastningerne omfatter en lineær algebra-rutine afledt af LINPACK, en hurtig Fourier-transformation, en algoritme for neurale net til vurdering af mønstre og en forbedret version af Livermore loops benchmark. JPEG-komprimering, en XML-parser, ZIP-komprimering og en 256-bit sikker hash-algoritme (SHA-256) udgør grundlaget for de heltalsbaserede arbejdsbelastninger.

MPFSO95T-modellerne af disse SoC-FPGA'er, som MPFS095TL-FCSG536E, kan levere op til 6.500 Coremarks ved 1,3 watt (figur 3).

Figur 3: MPFS095T FPGA SoC'en (orange linje) leverer 6500 Coremarks ved 1,3 watt. (Billedkilde: Microchip Technology)

Figur 3: MPFS095T FPGA SoC'en (orange linje) leverer 6500 Coremarks ved 1,3 watt. (Billedkilde: Microchip Technology)

Sikkerhedsovervejelser

De sikkerhedskritiske og hårde realtidsapplikationer til disse FPGA SoC'er kræver stærk sikkerhed ud over høj energieffektivitet og kraftig behandlingskapacitet. De grundlæggende sikkerhedsfunktioner i disse FPGA SoC'er omfatter DPA-resistent bitstream-programmering (Differential Power Analysis), en TRNG-generator (True Random Number Generator) og en PUF-funktion (Physically Unclonable Function). De omfatter også standard- og brugerdefineret sikker opstart, fysisk hukommelsesbeskyttelse, der giver begrænsninger i hukommelsesadgangen i forbindelse med maskinens privilegiestatus, herunder maskin-, supervisor- eller brugertilstand, og immunitet mod Meltdown- og Spectre-angreb.

Sikkerheden begynder med sikker styring af forsyningskæden, herunder brugen af hardware-sikkerhedsmoduler (HSM'er) under testning og pakning af waferne. Brugen af et 768-byte digitalt signeret x.509 FPGA-certifikat, der er indlejret i hver FPGA SoC, bidrager til sikring af forsyningskæden.

Disse FPGA SoC'er indeholder adskillige indbyggede manipulationsdetektorer for at sikre sikker og pålidelig drift. Hvis der registreres manipulation, udstedes der en manipulationsflag, som gør det muligt for systemet at reagere efter behov. Nogle af de tilgængelige manipulationsdetektorer omfatter:

- Spændingsmonitorer

- Temperatursensorer

- Detektorer for clockfejl og clockfrekvens

- JTAG aktiv detektor

- Mesh aktiv detektor

Sikkerheden er yderligere sikret med 256-bit avanceret krypteringsstandard (AES-256) symmetrisk blokchiffer korrelationseffektangreb (CPA) modforanstaltninger, integrerede kryptografiske digestfunktioner for at sikre dataintegritet, integreret PUF til nøgleopbevaring og nulstillingsfunktioner for FPGA-strukturen og alle on-chip hukommelser.

FPGA SoC-eksempler

Microchip Technology kombinerer disse muligheder og teknologier i PolarFire FPGA SoC'er med flere hastighedsgrader, temperaturklassificeringer og forskellige pakkestørrelser for at støtte designernes behov for en lang række løsninger med mellem 25 K og 460 K logiske elementer. Der findes fire temperaturklasser (alle klassificeret til TJ): 0 °C til +100 °C i det udvidede kommercielle område, -40 °C til +100 °C i det industrielle område, -40 °C til +125 °C i det automotive område og -55 °C til +125 °C i det militære område.

Designere kan vælge mellem enheder med standard hastighedskvalitet eller enheder med -1 hastighedskvalitet, der er 15 % hurtigere. Disse FPGA SoC'er kan drives ved 1,0 volt for at opnå den laveste effekt eller ved 1,05 volt for at opnå højere ydeevne. De er tilgængelig i en række forskellige pakkestørrelser, herunder 11 x 11 mm, 16 x 16 mm og 19 x 19 mm.

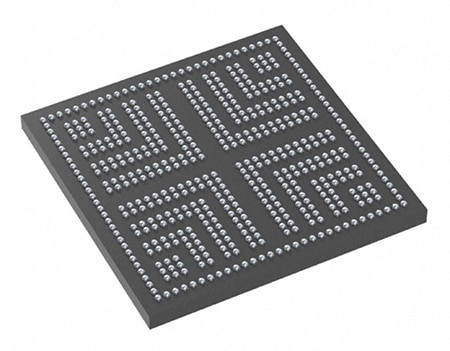

Til applikationer, der kræver udvidet drift ved kommercielle temperaturer, standardhastighed og 254 K logikelementer i en 19 x 19 mm pakke, kan designere bruge MPFS250T-FCVG484EES. For enklere løsninger, der kræver 23 K logikelementer, kan designere henvende sig til MPFS025T-FCVG484E, også med udvidet drift ved kommercielle temperaturer og standard hastighedskvalitet i en 19 x 19 mm pakke. MPFS250T-1FCSG536T2 med 254 K logikelementer er designet til højtydende bilsystemer og har et driftstemperaturområde fra -40 til 125 °C og en hastighedsklasse -1 for en 15 % hurtigere clock-hastighed i en kompakt 16 x 16 mm pakke med 536 kontaktpunkter med 0,5 mm afstand (Figur 4).

Figur 4: MPFS250T-1FCSG536T2 til bilindustrien leveres i en 16 x 16 mm stor pakke med 536 kontaktpunkter med 0,5 mm afstand. (Billedkilde: Microchip Technology)

Figur 4: MPFS250T-1FCSG536T2 til bilindustrien leveres i en 16 x 16 mm stor pakke med 536 kontaktpunkter med 0,5 mm afstand. (Billedkilde: Microchip Technology)

FPGA SoC udviklingsplatform

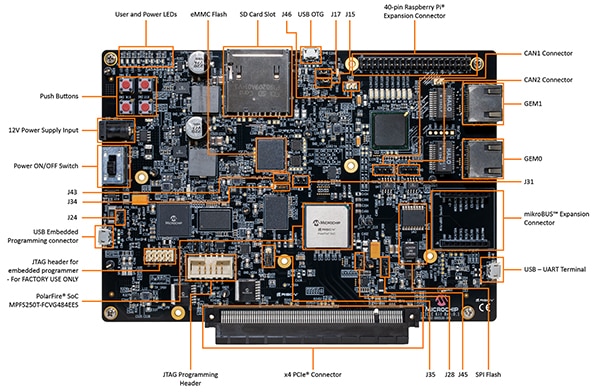

For at fremskynde designet af systemer med PolarFire FPGA SoC tilbyder Microchip MPFS-ICICICLE-KIT-ES PolarFire SoC Icicle-kit-ES, der gør det muligt at udforske det femkernede Linux-kapable RISC-V-mikroprocessorsubsystem med lav effekt og realtidsudførelse. Pakken indeholder en gratis Libero Silver-licens, som er nødvendig for at evaluere design. Det understøtter programmerings- og fejlfindingsfunktioner i et enkelt sprog.

Disse FPGA SoC'er understøttes af VectorBlox-accelerator softwareudviklingskit (SDK), som muliggør AI/ML-applikationer med lav effekt og lille formfaktor. Der lægges vægt på at forenkle designprocessen i en sådan grad, at designere ikke behøver at have tidligere erfaring med FPGA-design. VectorBlox-accelerator SDK gør det muligt for udviklere at programmere energieffektive neurale netværk ved hjælp af C/C++. Icicle-sættet har mange funktioner, der giver et omfattende udviklingsmiljø, herunder et multirail strømsensorsystem til overvågning af de forskellige strømdomæner, PCIe-rootport og indbyggede hukommelser - herunder LPDDR4, QSPI og eMMC Flash - til at køre Linux og Raspberry Pi samt mikroBUS-udvidelsesporte til et væld af muligheder for kablet og trådløs tilslutning samt funktionelle udvidelser som GNSS-placeringskapacitet (Figur 5).

Figur 5: Dette omfattende FPGA SoC-udviklingsmiljø omfatter stik til Raspberry Pi- (øverst til højre) og mikroBUS- (nederst til højre) udvidelseskort. (Billedkilde: Microchip Technology)

Figur 5: Dette omfattende FPGA SoC-udviklingsmiljø omfatter stik til Raspberry Pi- (øverst til højre) og mikroBUS- (nederst til højre) udvidelseskort. (Billedkilde: Microchip Technology)

Udvidelseskort

Et par eksempler på mikroBUS-udvidelseskort omfatter:

MIKROE-986, til tilføjelse af CAN-busforbindelse ved hjælp af en seriel perifer interface (SPI).

MIKROE-1582, til interface mellem MCU'en og en RS-232-bus.

MIKROE-989, til tilslutning til en RS422/485-kommunikationsbus.

MIKROE-3144 understøtter LTE Cat M1- og NB1-teknologierne, der muliggør pålidelig og enkel tilslutning til 3GPP IoT-enheder.

MIKROE-2670 muliggør GNSS-funktionalitet med samtidig modtagelse af GPS- og Galileo-konstellationer plus enten BeiDou eller GLONASS, hvilket giver høj positionsnøjagtighed i situationer med svage signaler eller interferens i bykløfter.

Konklusion

Designere kan anvende FPGA SoC'er til at udvikle forbundne, sikkerhedskritiske og deterministiske systemer i hård realtid. FPGA SoC'er indeholder en bred vifte af systemelementer, herunder en FPGA-struktur, RISC-V MCU-subsystem med højtydende hukommelse, interface til højhastighedskommunikation og adskillige sikkerhedsfunktioner. For at hjælpe designere med at komme i gang er tilgængelig udviklingskort og miljøer, der indeholder alle de nødvendige elementer, herunder udvidelseskort, der kan bruges til at implementere en lang række kommunikations- og lokaliseringsfunktioner.

Anbefalet læsning

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.