Hvorfor I2C-bussen (Inter-Integrated Circuit) gør det så let at forbinde integrerede kredsløb – og hvordan den bruges

Bidraget af DigiKeys nordamerikanske redaktører

2020-04-07

Kommunikation og kontrol på tværs af integrerede kredsløb (IC'er) med en parallel bus på et PCB er upraktisk. Selv en 8-bit processor ville kræve 16 linjer blot til data og mange flere til en adressebus. Det er endnu mere problematisk, hvis flere IC'er skal være på en delt kommunikationsbus. Der er ikke nok plads til alle de PCB-baner. Løsningen er at forbinde IC'er med en seriel kommunikationsbus såsom Inter-Integrated Circuit (I2C) bus, en seriel bus med to ledninger, der løser problemet.

Denne artikel beskriver I2C-bussens oprindelse, og hvordan den giver en effektiv serieforbindelse mellem IC'er. Det diskuteres dernæst, hvordan I2C-bussen implementeres fysisk, protokolstrukturen og almindelige anvendelsesområder for denne allestedsnærværende kommunikationsbus. Til demonstrationsformål bruges eksempler på I2C-grænseflader og -løsninger fra Microchip Technology. Artiklen diskuterer også lighederne og forskellene mellem I2C og System Management Bus (SMBus).

Hvad er I2C-bussen?

I2C-bussen blev udviklet i 1980'erne af Phillips Semiconductors, nu kendt som NXP Semiconductors, som en simpel tovejsbus med to ledere til effektiv kommunikation og kontrol af integrerede kredsløb på et fælles PCB. Den første specifikation stod klar i 1992, og bussen er siden blevet en de facto-standard i komponenter fra mere end 50 IC-producenter. Den store udbredelse baner vejen for en systemtilgang til design, hvor IC'er kan inkluderes i I2C-busstrukturen uden behov for et specialtilpasset design. Adskillige andre specialiserede busser, heriblandt SMBus og Power Management Bus (PMBus), deler den samme grundlæggende arkitektur.

I2C-bussen kan forbinde flere IC'er og sensorer, fordi det er en adresserbar bus; et adressefelt på syv eller ti bit gør det muligt at sende meddelelser fra master-enheden til en bestemt enhed. Den oprindelige I2C havde en maksimal clockfrekvens på 100 kilohertz (kHz), men i årenes løb har hurtigere driftstilstande gradvist flyttet grænsen til 3,4 megahertz (MHz).

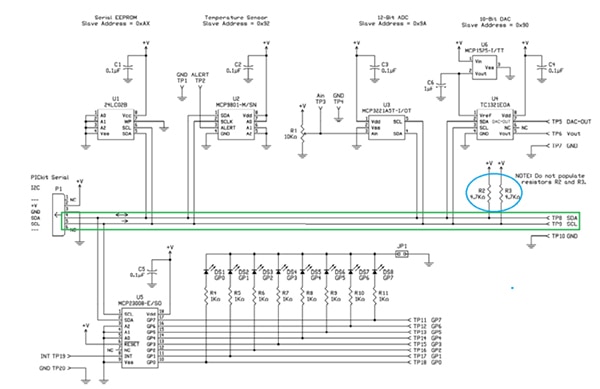

I2C-bussen bruger to ledere med betegnelserne SDA og SCL, hhv. serial data line og serial clock line. SDA og SCL er open drain-/åben kollektor-tovejslinjer og er forbundet til den positive strømbus via en strømkilde eller en pull-up-modstand. Det er muligt at tilslutte flere enheder til bussen – det maksimale antal er begrænset af bussens kapacitans. En master-enhed styrer bussen, og hver enhed på bussen har en entydig adresse. Master-enheden kan både sende og modtage data over bussen (figur 1). I2C understøtter multi-master-funktionalitet med registrering og håndtering af kollision for at forhindre, at to eller flere master-enheder starter dataoverførsler på samme tid. Denne artikel fokuserer dog på single-master-konfigurationer.

Figur 1: Skema over et demonstrations-PCB fra Microchip Technology, der anvender I2C-bussen og forbinder den til fem forskellige enheder. Master-enheden er ekstern via stik P1. SCL- og SDA-linjerne er markeret med grønt, og de to pull-up-modstande er markeret med blå cirkler. (Billedkilde: Microchip Technology)

Figur 1: Skema over et demonstrations-PCB fra Microchip Technology, der anvender I2C-bussen og forbinder den til fem forskellige enheder. Master-enheden er ekstern via stik P1. SCL- og SDA-linjerne er markeret med grønt, og de to pull-up-modstande er markeret med blå cirkler. (Billedkilde: Microchip Technology)

Figur 1 viser skemaet for et Microchip Technology PKSERIAL-I2C1 I2C-demonstrationskort. Kortet implementerer I2C-bussen med fem forskellige enheder, herunder en EEPROM, en temperaturføler, en 12-bit analog-til-digital-konverter (ADC), en 10-bit digital-til-analog-konverter (DAC), og en 8-bit seriel-til-parallel-konverter. Master-enheden er ikke på kortet og er tilsluttet via stik P1. SDA- og SCL-buslinjerne er markeret med grønt, og pull-up-modstandene er markeret med blå cirkler.

SDA- og SCL-niveauerne er generelt en fast procentdel af den positive forsyningsspænding – typisk mærket VDD. Referenceniveauerne er indstillet til 70 % og 30 % af VDD for logisk "1" (høj) og logisk "0" (lav), henholdsvis.

Clocksignaler forekommer i impulser med ét clocksignal for hver overført databit. Data på SDA-linjen skal være gyldige, mens clocksignalet er højt. Data kan kun ændres, mens clocksignalet er lavt.

For designere forenkles nye projekter, fordi I2C-grænsefladerne er integreret i IC'et, og der ikke er behov for at designe en grænseflade. Hver enhed etablerer ganske enkelt direkte forbindelse til bussen. IC'er kan tilføjes eller fjernes fra bussen uden at påvirke de andre kredsløb (såfremt det samlede antal IC'er ikke overstiger grænsen for kapacitans). Den simple bus med to ledere minimerer antallet af ben i hvert IC og antallet af baner på PCB'et.

I2C-protokollen

Bussen er 8-bit-orienteret og kommunikerer i bytes. Som nævnt var den oprindelige maksimale clockfrekvens 100 kHz i det, der nu kaldes Standard Mode. Bussen understøtter nu 400 kbps i Fast Mode, op til 1 Mbps i Fast Mode Plus, og op til 3,4 Mbps i High Speed Mode (Hs-Mode).

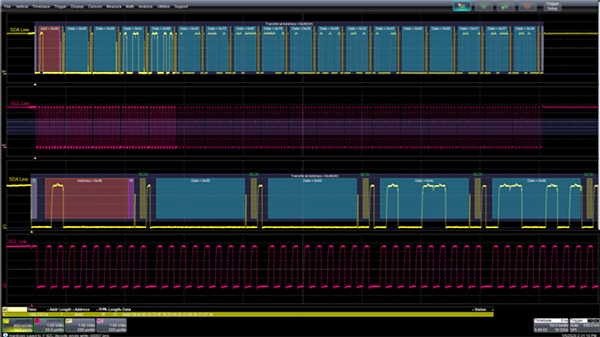

I2C-protokollen kan bedst illustreres ved at kigge nærmere på en typisk overførsel på bussen (figur 2). Kilden til skærmbilledet er et Teledyne LeCroy-oscilloskop med en lavhastigheds seriel datatrigger og -dekoderfunktionalitet WS4KHD-EMB TD. Denne oscilloskopfunktion kan udløse og dekode op til 19 lavhastigheds serielle datagrænseflader inklusive I2C.

Figur 2: En typisk I2C-datapakke bestående af en startbit, et adressefelt, godkendelsesbit, 17 databyte med hver sin ACK-bit – og endelig en stopbit. Hvert felt er identificeret med en farvekodet overlejring. Den øverste (gule) aftegning er hele SDA-pakken – nedenunder vises SCL-clocksignalet (rød). Tredje og fjerde aftegning er vandret udvidede visninger af begge signaler. (Billedkilde: DigiKey)

Figur 2: En typisk I2C-datapakke bestående af en startbit, et adressefelt, godkendelsesbit, 17 databyte med hver sin ACK-bit – og endelig en stopbit. Hvert felt er identificeret med en farvekodet overlejring. Den øverste (gule) aftegning er hele SDA-pakken – nedenunder vises SCL-clocksignalet (rød). Tredje og fjerde aftegning er vandret udvidede visninger af begge signaler. (Billedkilde: DigiKey)

Oscilloskopet kan udløses ved specifikke serielle hændelser, herunder start, stop, manglende godkendelse (ACK), adresse, data, adresse plus data, billedlængde og EEPROM-dataoverførsel. Protokolelementerne af den serielle datastandard er markeret med en farvekodet overlejring. Hvert protokolfelt dekodes enten som binære, heksadecimale værdier eller ASCII-værdier med den valgte kode vist inden for overlejringen.

SDA-signalet vises som en gul aftegning, mens SCL-signalet vises som en rød aftegning. De grå overlejringsfelter angiver start- og stopfunktionerne. Den murstensrøde overlejring markerer adressedata, de blå felter er pakkedata, og de olivengrønne markerer ACK-funktionerne.

Den øverste overlejring viser hele I2C SDA-pakken fra start til stop. Lige under den er det tilsvarende SCL-signal. Den tredje aftegning fra oven er en tidsmæssigt udvidet, zoomet visning af SDA-signalet, og nedenunder er det synkrone SCL-signal.

Både SDA- og SCL-linjen hviler i den høje tilstand mellem overførslerne, når bussen er ledig. SCL-signalet består af ni impulser ved clockfrekvensen, én for hver databit overført, og en ekstra for ACK-bitten.

Alle bustransaktioner starter med en master-genereret startbit vist i den zoomede SDA-aftegning som et gråt overlejringsfelt. Starten angives, ved at masteren trækker SDA-linjen lav, mens SCL-linjen er i høj tilstand. Når masteren har udsendt startbitten, regnes bussen for optaget. Masteren kan udsende flere starter, en situation hvor de efterfølgende starter ofte kaldes genstarter.

Alle dataoverførsler har en længde på 8 bit (én byte) efterfulgt af en ACK-bit. Bit sendes med den vigtigste bit (MSB, most significant bit) først. Hver byteoverførsel skal godkendes. Hvis slave-enheden er optaget og ikke kan modtage eller sende data, kan den trække SCL-linjen lav. Det tvinger master-enheden i en ventetilstand, indtil slave-enheden frigiver SCL-linjen.

ACK-bitten formes, når afsenderenheden frigiver SDA-linjen inden den niende clockimpuls (godkendelsen). Hvis modtagerenheden har modtaget databyten, trækker den SDA-linjen lav. I den zoomede visning af SDA-linjen på figur 2 er der en smal spids lige inden den niende clockimpuls – det er SDA-linjen, der frigives for at vende tilbage til høj tilstand. Modtageren trækker SDA-linjen, der genererer ACK-signalet ned – det er symbolsk markeret med den olivengrønne overlejring. Hvis modtageren ikke trækker SDA-linjen ned inden den niende clockimpuls, er det en ikke-godkendelses-respons (NACK, not acknowledge). Hvis der opstår en NACK, kan masteren enten generere et stopsignal og afbryde overførslen eller udsende en ny start for at prøve igen.

Umiddelbart efter starttilstanden, udsendes en slave-adresse. Det er angivet med et murstensrødt overlejringsfelt. Der er to mulige adresseformater – 7 bit eller 10 bit – hvoraf 7-bit adressen er den mest almindelige. De første 7 bit efter start repræsenterer adressedataene. Den 8. bit angiver dataretningen – enten læse eller skrive. En skrivehandling indikeres, ved at SDA-linjen er i lav tilstand, og en læsehandling indikeres, ved at SDA-linjen er i høj tilstand. Ved 10-bit adresser bruges de to første byte efter starttilstanden. I2C reserverer adskillige adresser til interne funktioner. Dekodningsadressedataene vises i adresseoverlejringsfeltet i binært format, heksadecimalt format eller ASCII-format.

De blå overlejringsfelter markerer dataoverførslerne. Hver af dem er otte bit lang og efterfølges af en ACK/NACK-respons. Antallet af databyte i en I2C-pakke er ubegrænset, men figur 2 indeholder 17. De dekodede data vises i dataoverlejringsfeltet, ligesom adressedekodningen. Datastrømmen efterfølges af en master-genereret stopbit i slutningen af dataoverførslen, indikeret med et gråt overlejringsfelt i den øverste dataaftegning. Stopbitten er en lav-til-høj-overgang på SDA-linjen mens SCL-linjen er i høj tilstand. Efter stopsignalet er bussen igen ledig.

Tabellen i bunden af skærmbilledet opsummerer alle oplysningerne om den relaterede datapakke, inklusive tid siden start (trigger), adresselængde, adresse, læse- eller skrivehandling, pakkelængde og en oversigt over dataindholdet. Antallet af poster i tabellen stemmer overens med antallet af I2C-pakker registreret af oscilloskopet – hvilket i dette tilfælde kun er en enkelt linje.

Hvis der opstår en protokolfejl, angives det med et lys rødt felt bag de andre protokoloverlejringsfelter.

I2C-enheder

En af de største fordele ved I2C-bussen er det ekstremt høje antal enheder, der har indarbejdet den i deres design. Microchip Technologies-demonstrationskortet giver nogle eksempler på IC-typerne, der har indarbejdet I2C-bussen eller en af dens afledninger, såsom SMBus.

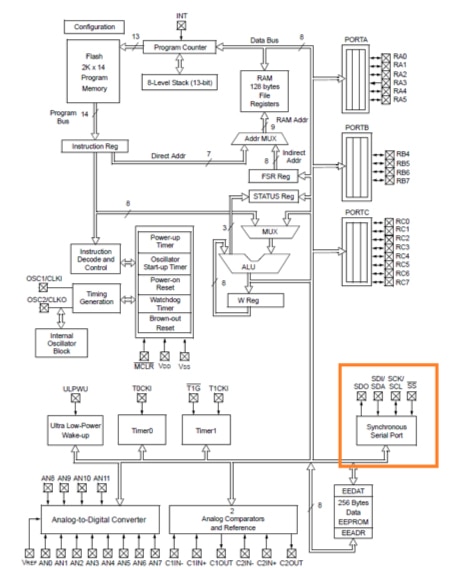

Microchip Technologys PIC16F677 er en 8-bit mikrocontroller, der benyttes i mange integrerede design. Den implementerer en synkron seriel port, der kan bruges til at kommunikere med enten SPI'en (serial peripheral interface) eller mellem I2C og andre controllere eller tilbehørsenheder (figur 3).

Figur 3: Microchip Technology PIC16F677 er en 8-bit mikrocontroller, der omfatter en synkron seriel port (markeret med orange), der kan programmeres som enten en SPI- eller en I2C-bus. (Billedkilde: Microchip Technology)

Figur 3: Microchip Technology PIC16F677 er en 8-bit mikrocontroller, der omfatter en synkron seriel port (markeret med orange), der kan programmeres som enten en SPI- eller en I2C-bus. (Billedkilde: Microchip Technology)

Mikrocontrolleren understøtter både I2C master- og slave-tilstand med 7-bit eller 10-bit adresseformat. Den bruger SCK/SCL-benet til I2C SCL-clocksignalet og SDI/SDA-benet til datasignalet.

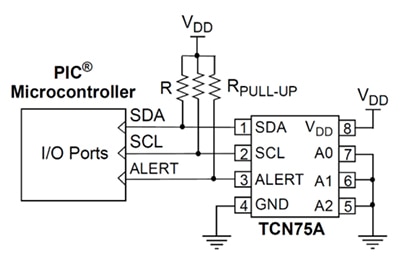

Disse to ben er forbundet med SCL- og SDA-linjerne på I2C-bussen for at muliggøre kommunikation med andre enheder. En almindelig forbindelse er til en I2C-baseret sensor som f.eks. Microchip Technologys TCN75AVOA713 serielle temperatursensor med to ledere (figur 4).

Figur 4: Microchip Technology TCN75A-temperaturføleren er direkte forbundet med PIC16F677-mikrocontrolleren for at kommunikere temperaturdata. (Billedkilde: Microchip Technology)

Figur 4: Microchip Technology TCN75A-temperaturføleren er direkte forbundet med PIC16F677-mikrocontrolleren for at kommunikere temperaturdata. (Billedkilde: Microchip Technology)

Takket være muligheden for seriel kommunikation har denne temperaturføler øget funktionalitet. Dens interne brugerprogrammerbare registre kan bruges til at indstille opløsningen for temperaturmålinger og nedlukningstilstand ifm. strømbesparelse – og sågar til at indstille alarmoutputtet til at angive, når temperaturområdet overstiger de på forhånd angivne grænseværdier.

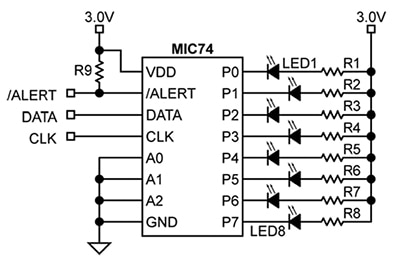

Der er også en række enheder, der kan dekode den serielle I2C-datastrøm og bryde den op i parallelle data. Se f.eks. Microchip Technology MIC74YQS-TR I/O-ekspanderen med 2 ledere og ventilatorstyring (figur 5).

Figur 5: Microchip Technology MIC74YQS-TR I/O-ekspanderen konverterer en seriel datastrøm til otte uafhængige parallelle I/O-linjer. (Billedkilde: Microchip Technology)

Figur 5: Microchip Technology MIC74YQS-TR I/O-ekspanderen konverterer en seriel datastrøm til otte uafhængige parallelle I/O-linjer. (Billedkilde: Microchip Technology)

Dette IC er en fuldt programmerbar I/O-ekspander med otte uafhængige I/O-linjer. I/O-linjerne kan programmeres individuelt som input eller output. Figur 5 viser MIC74YQS-TR, der driver otte LED'er under den serielle bus' kontrol. Det minder om brugen af MCO23008 på I2C-demonstrationskortet i figur 1. MIC74YQS-TR kan sammen med en effektregulator også implementere en hastighedsregulator til en blæsermotor med sine fire vigtigste bit.

SMBus og I2C

Det serielle input til I/O-ekspanderen er designet til SMBus, men er også kompatibelt med I2C-bussen. SMBus-specifikationen er baseret på I2C og blev defineret af Intel og Duracell i 1994. Den primære forskel er, at I2C-logikniveauer i standardtilstand er i forhold til VDD, og logikniveauerne for SMBus er faste. I de fleste tilfælde hvor VDD er mellem 3-5 volt, viser erfaringen, at dette ikke er noget problem.

En anden forskel er, at SMBus er begrænset til clockfrekvenser på 100 kHz eller lavere, mens I2C har flere tilstande, der understøtter højere clockfrekvenser. I forbindelse med bus-kompatibilitet begrænser det den maksimale clockfrekvens til 100 kHz eller I2C standard-clocktilstanden.

Så med undtagelse af nogle meget specielle situationer er SMBus og I2C kompatible med hinanden.

Konklusion

I2C-bussen og dens afledninger findes i hundredvis af IC-typer, så det er let at forbinde dem til mange forskellige design og anvendelsesformål. Kobling af sensorer med blandet signal og analoge sensorer udvider mulighederne med mikrocontrollerbaserede integrerede systemer. Alt dette via en enkel seriel, digital grænseflade med to ledere.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.