Sådan designer og certificerer du funktionelt sikre RTD-baserede systemer

Bidraget af DigiKeys nordamerikanske redaktører

2023-07-24

En modstandstemperaturdetektor (RTD), der består af en transducer og dens analoge front-end (AFE) signalbehandlingskredsløb, er meget udbredt, nøjagtig og pålidelig. Men til missionskritiske og højpålidelige applikationer er det ofte nødvendigt at designe og sikre et funktionelt sikkert system via Route 1S- eller Route 2S-komponentcertificeringsprocessen.

At certificere et system for funktionel sikkerhed er en kompleks proces, da alle komponenter i systemet skal gennemgås for potentielle fejltilstande og -mekanismer. Der er forskellige metoder til at diagnosticere fejl, og ved at bruge dele, der allerede er certificeret, lettes denne arbejdsbyrde sammen med certificeringsprocessen.

Bemærk, at "pålidelighed" er relateret til, men ikke det samme som funktionel sikkerhed. I sin enkleste form henviser pålidelig til et design og en implementering, der fungerer i henhold til specifikationerne uden problemer eller fejl, mens "funktionelt sikker" betyder, at eventuelle fejl skal opdages af designet. Der er brug for både pålidelighed og funktionel sikkerhed til kritiske applikationer.

Denne artikel vil se på det grundlæggende i RTD'er og deres signalbehandlingskredsløb i forbindelse med funktionelt sikker certificering. Derefter diskuteres de forskellige niveauer af pålidelighed og fejlcertificering, og hvad der kræves for at opfylde dem via begge veje. To flerkanals RTD AFE-IC'er, AD7124-parret fra Analog Devices, sammen med et tilhørende evalueringskortarrangement, vil blive brugt til at illustrere de vigtigste punkter.

Den funktionelle sikkerheds rolle

Den funktionelle sikkerheds rolle er at sikre frihed fra uacceptabel risiko for personskade eller skade på menneskers helbred gennem korrekt implementering af en eller flere automatiske beskyttelses-/sikkerhedsfunktioner. Det sikrer, at produktet, enheden eller systemet fortsætter med at fungere sikkert, hvis der opstår en fejlfunktion. Det er nødvendigt i en bred vifte af industrielle, kommercielle og endda nogle forbrugerapplikationer, såsom:

- Autonome køretøjer

- Maskinsikkerhed og robotteknologi

- Industrielle kontrolsystemer (ICS)

- Smart-hjem-produkter til forbrugere

- Smart-fabrikker og distributionskæder

- Sikkerhedsinstrumenterede systemer og kontrolsystemer til farlige steder

I et funktionelt sikkert design vil en hovedafbryder f.eks. stadig kunne slukke for strømmen, selv hvis andre komponenter i systemet svigter (figur 1).

Figur 1: I et funktionelt sikkert system kan der ikke være nogen tvivl om, at denne kontakt gør det, den er designet til at gøre. (Billedkilde: Pilla via City Electric Supply Co.)

Figur 1: I et funktionelt sikkert system kan der ikke være nogen tvivl om, at denne kontakt gør det, den er designet til at gøre. (Billedkilde: Pilla via City Electric Supply Co.)

Grundlæggende om RTD

Hvorfor se på temperatur og funktionel sikkerhed? En god grund er, at temperatur er den mest almindeligt målte fysiske parameter. Det er ofte relateret til sikkerhed eller kritiske applikationer, og det understøttes af et bredt udvalg af transducere. Blandt disse er RTD'er, som konceptuelt er enkle: De udnytter den kendte og repeterbare temperaturkoefficient for modstand (TCR) for metaller som nikkel, kobber og platin. Platin-RTD'er med 100 ohm (Ω) og 1000 Ω modstand ved 0 °C er de mest udbredte og kan bruges i området fra -200 °C til +850 °C.

Disse RTD'er har et meget lineært forhold mellem modstand og temperatur over dette temperaturområde; til situationer med ultrahøj nøjagtighed er der korrektions- og kompensationstabeller og faktorer, der kan anvendes. Platin-RTD'en med en nominel modstand på 100 Ω (betegnet som PT100) har en typisk modstand på 18 Ω ved -200 °C og 390,4 Ω ved +850 °C.

Brug af en RTD kræver, at den exciteres af en kendt strøm, der normalt holdes på omkring 1 milliampere (mA) for at minimere selvopvarmning. Der bruges også andre strømværdier, afhængigt af den nominelle RTD-modstand.

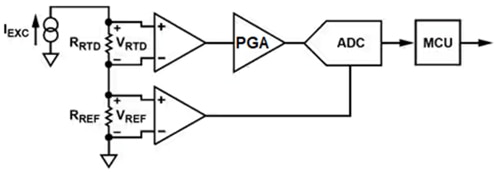

Spændingsfaldet over RTD'en måles samtidig via en AFE, der består af en PGA (programmable-gain amplifier) og i næsten alle tilfælde en ADC (analog-til-digital konverter) i forbindelse med en MCU (mikrocontroller enhed) (figur 2).

Figur 2: At bruge en RTD til at måle temperatur kræver, at man sender en kendt strøm gennem RTD'en og måler spændingsfaldet over den og derefter anvender Ohms lov. (Billedkilde: Digi-Key)

Figur 2: At bruge en RTD til at måle temperatur kræver, at man sender en kendt strøm gennem RTD'en og måler spændingsfaldet over den og derefter anvender Ohms lov. (Billedkilde: Digi-Key)

Kredsløbstopologien i dette grundlæggende system er identisk med brugen af en følermodstand til at bestemme strømmen gennem en belastning, men her er de kendte og ukendte variabler byttet om. Ved strømmåling er modstanden kendt, mens strømmen er ukendt, så beregningen er I = V/R. For RTD'er er strømmen kendt, men det er modstanden ikke, så beregningen er R = V/I.

PGA'en er nødvendig for at opretholde signalintegriteten og maksimere dynamikområdet, da spændingsniveauerne over RTD'en kan variere fra ti millivolt til hundredvis af millivolt, afhængigt af RTD-typen og temperaturen.

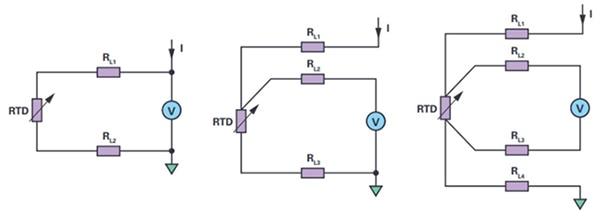

Den fysiske forbindelse mellem excitationskilden, RTD'en og PGA'en kan være et interface med to, tre eller fire ledninger. Selvom to ledninger i princippet er tilstrækkeligt, er der problemer med IR-fald i forbindelsesledningerne sammen med andre artefakter. Brug af tre- og firetrådstopologier i en mere avanceret Kelvin-forbindelse resulterer i mere præcis og ensartet ydeevne, selvom det øger ledningsomkostningerne (figur 3).

Figur 3: RTD'en kan drives og måles via kun to ledninger (venstre), men brugen af tre ledninger (midten) og endda fire ledninger (højre, Kelvin-forbindelse) gør det muligt at eliminere forskellige fejlkilder på grund af ledningerne. (Billedkilde: Analog Devices)

Figur 3: RTD'en kan drives og måles via kun to ledninger (venstre), men brugen af tre ledninger (midten) og endda fire ledninger (højre, Kelvin-forbindelse) gør det muligt at eliminere forskellige fejlkilder på grund af ledningerne. (Billedkilde: Analog Devices)

Begynd med terminologi og standarder

Som med mange andre specialer har funktionel sikkerhed mange unikke termer, datasæt og akronymer, der bruges i vid udstrækning i relaterede diskussioner. Blandt disse er:

- Fejl over tid (FIT, Failures-in-time): antallet af fejl, der kan forventes i løbet af en milliard (109) timers drift af enheden.

- Fejltilstande og effektanalyse (FMEA, Failure modes and effects analysis): Processen med at gennemgå så mange komponenter, samlinger og undersystemer som muligt for at identificere potentielle fejltilstande i et system og deres årsager og virkninger.

- Fejltilstande, effekter og diagnostiske analyser (FMEDA, Failure modes effects and diagnostic analyses): En systematisk analyseteknik til at opnå fejlrater, fejltilstande og diagnostisk kapacitet på delsystem-/produktniveau.

FIT-data er nødvendige sammen med FMEDA'er på de forskellige komponenter i systemet for en komplet analyse. FMEA giver kun kvalitative oplysninger, mens FMEDA giver både kvalitative og kvantitative oplysninger, så brugerne kan måle et niveau af kritikalitet for fejltilstande og ordne dem efter vigtighed. FMEDA tilføjer risiko, fejltilstande, effekter og diagnostisk analyse samt information om pålidelighed.

- Sikkerhedsintegritetsniveau (SIL, Safety Integrity Level): Der er fire diskrete integritetsniveauer forbundet med SIL: SIL 1, SIL 2, SIL 3 og SIL 4. Jo højere SIL-niveau, jo højere er det tilknyttede sikkerhedsniveau, og jo mindre er sandsynligheden for, at et system ikke fungerer korrekt.

En SIL 2-klassificering angiver, at over 90 % af fejlene i systemet kan diagnosticeres. For at certificere et design skal systemdesigneren fremlægge dokumentation for certificeringshuset om de potentielle fejl, om disse er sikre fejl eller farlige fejl, og hvordan fejlene kan diagnosticeres.

- IEC 61508, med den formelle titel "Functional Safety of Electrical/Electronic/Programmable Electronic Safety-related Systems" (Funktionel sikkerhed af elektriske/elektroniske/programmerbare elektroniske sikkerhedsrelaterede systemer), (og uformelt blot kaldet "Electronic Functional Safety” (Elektronisk funktionel sikkerhed)), er specifikationen for funktionelt sikre designs. Den dokumenterer det designflow, der er nødvendigt for at udvikle en SIL-certificeret del. Der skal genereres dokumentation for hvert trin, fra koncept og definition til design, layout, fremstilling, montering og test.

Denne proces er kendt som Route 1S og er kompliceret. Der findes dog et alternativ til Route 1S, som kaldes Route 2S-flowet. Dette er en "gennemprøvet i brug"-rute og er anvendelig, når store mængder af produktet er blevet designet til slutprodukter og systemer og bliver brugt i marken med tusindvis af timers akkumuleret drift.

Under Route 2S-flowet kan et produkt stadig certificeres ved at fremlægge dokumentation for certificeringsmyndigheden for:

- Mængder brugt i marken

- Analyse af eventuelle returneringer fra marken og detaljer om, at returneringerne ikke skyldtes fejl i selve komponenten.

- Sikkerhedsdatablad med detaljer om diagnostik og den dækning, de giver

- Ben og chip FMEDA

Sammenlægning af RTD-interface med SIL Route 2S-flowet

At certificere et system er en lang proces, da alle komponenter i systemet skal gennemgås for potentielle fejlmekanismer, og der er forskellige metoder til at diagnosticere fejl. Brug af dele, der allerede er certificeret, reducerer den nødvendige indsats og forkorter certificeringsprocessen.

En højt integreret, moden RTD-interfacekomponent er nøglen til at lette Route 2S-certificering, da den definerer en komplet løsningspakke og dermed kan karakteriseres fuldt ud med data, der er forbundet med feltbrug og fejl. Dette er i modsætning til brugen af flere mindre byggeklods-IC'er, hvor deres forskellige interfacer og interaktioner skal analyseres for den specifikke sammenkoblingskonfiguration, der bruges.

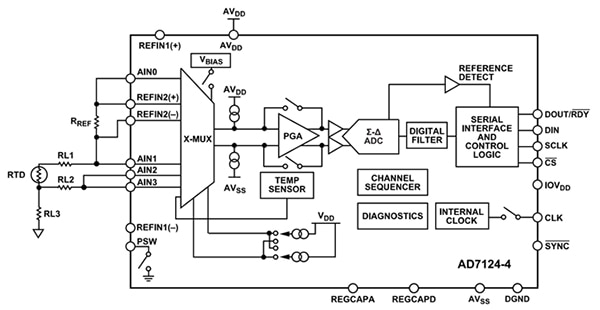

Et eksempel på dette er den firekanals AD7124-4 (figur 4) og den tilsvarende ottekanals AD7124-8 (fremover omtalt som "AD7124", når vi diskuterer de mange funktioner, de har til fælles). Disse komponenter passer godt til Route 2S-flowet på grund af deres indbyggede selvtest- og diagnosticeringsfunktioner samt deres "track record" i marken.

Figur 4: Den fire-kanals AD7124-4 er en funktionelt komplet RTD-sensor-til-processor-signalkæde. (Billedkilde: Analog Devices)

Figur 4: Den fire-kanals AD7124-4 er en funktionelt komplet RTD-sensor-til-processor-signalkæde. (Billedkilde: Analog Devices)

Disse IC'er er komplette løsninger til multikanals RTD-måling og indeholder alle de nødvendige byggesten fra en sensor til et digitaliseret output og til kommunikation med en tilhørende mikrocontroller. De omfatter multikanal-multiplexer, PGA, 24-bit sigma-delta ADC, strømkilder til RTD'erne, spændingsreferencer til intern drift, systemur, analog og digital filtrering og serielle interfacer med tre eller fire ledninger til SPI, QSPI, MICROWIRE og DSP-kompatible sammenkoblinger.

Tilstedeværelsen af disse funktioner giver dog ikke i sig selv grundlag for SIL Route 2S-kvalifikation. For at opnå et funktionelt sikkert design kræves der en række indlejrede diagnoser til de mange funktioner, der udgør RTD-systemet. De mange indlejrede diagnoser i AD7124 minimerer både designkompleksiteten og designtiden og fjerner behovet for at duplikere signalkæden for diagnosedækning.

Disse diagnoser omfatter, men er ikke begrænset til, overvågning af strømforsyningen, referencespændingen og den analoge indgang; detektering af en åben ledning til RTD'erne; kontrol af konverterings- og kalibreringsydelsen; kontrol af signalkædens funktionalitet; overvågning af læse-/skrivefunktionerne; og overvågning af registerindholdet.

Hvordan omsættes disse "high level"-udsagn til den nødvendige on-chip-diagnostik? Der er mange facetter i svaret, blandt andet:

SPI-diagnostik: For hver skrivning til AD7124 genererer processoren en CRC-værdi (Cyclic Redundancy Check), som føjes til den information, der sendes til ADC'en. ADC'en genererer derefter sin egen CRC-værdi ud fra de modtagne oplysninger og sammenligner den med den CRC-værdi, der er modtaget fra processoren. Hvis begge værdier stemmer overens, er informationen intakt og vil blive skrevet til det relevante on-chip-register.

Hvis værdierne ikke stemmer overens, betyder det, at der er sket en korruption i et bit på transmissionen, og IC'en sætter et fejlflag, der indikerer, at der er sket datakorruption. AD7124 beskytter sig også selv ved ikke at skrive den korrupte information ind i et register.

En lignende CRC-procedure bruges, når information læses fra AD7124 til systemprocessoren. Endelig tæller interfacen også clockpulser for at sikre, at der kun er otte sådanne pulser med hver læse- eller skrivedataramme, hvilket sikrer, at der ikke er opstået en clockglitch.

Kontrol af hukommelse: En CRC bruges også til at validere registerindhold ved opstart, eller når on-chip-registre ændres (f.eks. når forstærkningen ændres). CRC-processen udføres også med jævne mellemrum for at sikre, at ingen hukommelsesbit er blevet "flippet" på grund af støj eller andre årsager. Hvis der sker en ændring, og processoren efterfølgende får besked om, at registerindstillingerne er blevet ødelagt, kan den nulstille ADC'en og genindlæse registrene.

Kontrol af signalkæden: Alle kritiske statiske spændinger kan kontrolleres via ADC'en, herunder strømforsyningsskinner, LDO-regulatorudgange (lav-dropout) og referencespændinger; tilstedeværelsen eller fraværet af den eksterne kondensator over LDO'en kan også kontrolleres. Desuden kan man lægge en kendt spænding på ADC-indgangen for at kontrollere ADC'en og forstærkningsfunktionens indstillinger. Desuden kan kendte strømme injiceres over de analoge indgange for at kontrollere, om RTD'en er åben eller kortsluttet.

Konvertering og kalibrering: Resultaterne af ADC-konverteringen kontrolleres løbende for at se, om de går til alle nuller eller fuld skala, hvilket i begge tilfælde indikerer et problem. Bitstrømmen fra modulatoren i kernen af ADC'en overvåges for at sikre, at den ikke er mættet, og hvis der opstår mætning (hvilket betyder, at der har været 20 på hinanden følgende ettaller eller nuller fra modulatoren), sættes et fejlflag.

Masterclock-frekvens: Frekvensen på dette ur styrer ikke kun konverteringshastighederne, men fastlægger også hakfrekvenserne for de digitale filtre på 50/60 Hertz (Hz). Et internt register i AD7124 gør det muligt for den medfølgende processor at tage tid og dermed kontrollere nøjagtigheden af masterclocken.

Yderligere funktioner: AD7124 indeholder en temperatursensor, som også kan bruges til at overvåge chip-temperaturen. Begge versioner har en 4 kilovolt (kV) elektrostatisk afladningsklassificering (ESD) for robust ydeevne, og begge er indkapslet i en 5 × 5 millimeter (mm) LFCSP-pakke, der er velegnet til egensikre designs.

På grund af AD7124-4's og AD7124-8's interne kompleksitet, sofistikering og avancerede selvtestfunktioner giver det mening at have et middel til at træne og evaluere IC'erne.

For at opnå dette tilbyder Analog Devices et par forbundne kort: evalueringskortet EVAL-AD7124-4SDZ til AD7124-4 (figur 5) og det ledsagende EVAL-SDP-CB1Z SDP (System Demonstration Platform)/Interfacekort (figur 6). Den første er specifik for AD7124-4 og fungerer sammen med den anden, som giver kommunikation med brugerens pc og evalueringssoftware via et USB-link.

Figur 5: EVAL-AD7124-4SDZ er et evalueringskort til AD7124-4. (Billedkilde: Analog Devices)

Figur 5: EVAL-AD7124-4SDZ er et evalueringskort til AD7124-4. (Billedkilde: Analog Devices)

Figur 6: EVAL-SDP-CB1Z/Interfacekort er en ledsager til EVAL-AD7124-4SDZ-evalueringskortet, der giver en USB-forbindelse til en værts-pc. (Billedkilde: Analog Devices)

Figur 6: EVAL-SDP-CB1Z/Interfacekort er en ledsager til EVAL-AD7124-4SDZ-evalueringskortet, der giver en USB-forbindelse til en værts-pc. (Billedkilde: Analog Devices)

Evalueringsarrangementet understøttes af AD7124-4 EVAL+-softwaren, som fuldt ud konfigurerer AD7124-4-enhedens registerfunktionalitet og træner IC'en. Det giver også tidsdomæneanalyse i form af bølgeformsgrafer, histogrammer og tilhørende støjanalyse til evaluering af ADC-ydelsen.

Overgang til funktionelt sikkert design

Det er vigtigt at indse, at AD7124-4 og AD7124-8 ikke er SIL-klassificerede, hvilket betyder, at de ikke er designet og udviklet ved hjælp af udviklingsretningslinjer som defineret i IEC 61508-standarden. Men ved at forstå slutanvendelsen og ved at bruge de forskellige diagnoser korrekt, kan de vurderes til brug i et SIL-klassificeret design.

Vejen til Route 1S-certificering har flere overvejelser om analyse og håndtering af fejl, som kan være systemiske eller tilfældige. Systemiske fejl skyldes design- eller produktionsfejl, f.eks. et støjende interrupt på grund af manglende filtrering på det eksterne interruptben eller utilstrækkelig tolerance for et signal. I modsætning hertil skyldes tilfældige fejl fysiske årsager som korrosion, termisk stress eller slitage.

Et vigtigt problem kaldes den farlige uopdagede fejl, som behandles med flere teknikker. For at minimere tilfældige fejl bruger designere en eller alle tre taktikker:

- Mere pålidelige, mindre belastede komponenter.

- Diagnostik, der er afhængig af indbyggede detekteringsmekanismer implementeret via hardware eller software.

- Fejltolerance via redundante kredsløb. Ved at tilføje en redundant sti kan en enkelt fejl tolereres. Dette kaldes et hardware fejltolerancesystem (HFT1, Hardware Fault Tolerance), hvilket betyder, at én fejl ikke kan få systemet til at svigte.

Et værktøj til at forstå SIL-niveauets dækning er en matrix, der plotter sikker fejlfraktion (SFF) (mængden af diagnostisk dækning) og hardwarefejltolerance (redundansen) (Figur 7).

|

|||||||||||||||||||||||

Figur 7: Denne matrix karakteriserer sikker fejlfraktion (SFF) i forhold til hardwarefejltolerance (HFT) og giver indsigt i SIL-dækning. (Billedkilde: Analog Devices)

Rækkerne viser mængden af diagnostisk dækning, mens kolonnerne viser hardwarefejltolerancen. En HFT på 0 betyder, at hvis der opstår én fejl i systemet, vil sikkerhedsfunktionen gå tabt. Et højere diagnosticeringsniveau reducerer den nødvendige mængde systemredundans eller forbedrer SIL-niveauet for løsningen med det samme redundansniveau (nedad i matrixen).

Bemærk, at FMEDA for en typisk temperaturanvendelse med disse enheder viser en sikker fejlfraktion (SFF) på mere end 90 % i henhold til IEC 61508. To traditionelle ADC'er ville normalt være nødvendige for at give dette dækningsniveau via redundans, men AD4172 kræver kun en enkelt ADC, hvilket giver betydelige besparelser i styklisteomkostninger og printkortplads.

Dokumentation for SIL-klassificerede designs

Der kræves omfattende dokumentation for at opnå Route 1S-certificering. Blandt de nødvendige kildedokumenter er:

- Sikkerhedsdatablad (sikkerhedsmanualen for en SIL-klassificeret del)

- Ben FMEDA og chip FMEDA, med fejltilstande, effekter og analyse for begge dele

- Bilag F tjekliste (defineret af IEC 61508)

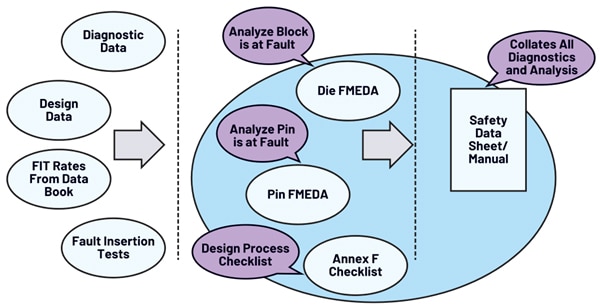

Denne dokumentation kommer igen fra en række forskellige kilder (figur 8):

- Diagnostiske data fra databladet indfanger alle de diagnostiske funktioner, der er tilgængelige i delen.

- Designdata refererer til interne data. For eksempel chip-arealet og effekten af hver intern blok i emnet.

- FIT, med satser for forskellige komponenter, er tilgængelige fra databogen.

- Fejlindsættelsestest udføres for blokke, der ikke kan analyseres ved hjælp af design- og diagnosedata. Disse tests planlægges ud fra applikationskravene, og resultatet af fejlindsættelsestestene bruges til at styrke FMEDA- og FMEA-dokumenterne.

Figur 8: De forskellige dokumentationskilder samles og trækkes igennem for at give den komplette informationspakke, der er nødvendig for SIL-certificering. (Billedkilde: Analog Devices)

Figur 8: De forskellige dokumentationskilder samles og trækkes igennem for at give den komplette informationspakke, der er nødvendig for SIL-certificering. (Billedkilde: Analog Devices)

Vi ser nærmere på detaljerne:

- Sikkerhedsmanualen eller sikkerhedsdatabladet bruger alle de indsamlede oplysninger til at give de nødvendige krav for at muliggøre integration af AD7124-4 eller AD7124-8. Den samler alle de diagnoser og analyser, der strømmer ind fra forskellige dokumenter og datasæt.

- Chip FMEDA for AD7124-4 og AD7124-8 analyserer de vigtigste blokke i applikationsskemaet, identificerer fejltilstande og -effekter og kontrollerer diagnosen og analyserne for en bestemt sikkerhedsfunktion. For eksempel viser analysen af urmodulet fejltilstande, effekten af hver enkelt på output, mængden af diagnostisk dækning og en analyse af påvirkningen (figur 9).

|

Figur 9: Denne tabel definerer masterclock-blokkens fejltilstand, effekter, diagnostik og analyse. (Billedkilde: Analog Devices)

Denne chip FMEDA resulterer i en kvantitativ præsentation af fejlrater for sikre fejl, farlige opdagede fejl og farlige uopdagede fejl. Alle disse bruges til at beregne SFF.

Ben FDEMA ser på fejl fra et andet perspektiv. Den analyserer forskellige typer fejl på AD7124-4's og AD7124-8's ben og deres konsekvenser for RTD-applikationen. Den gør dette for hver enkelt ben og beskriver resultatet for det tilfælde, hvor benet er åbent, kortslutter til forsyning/jord eller kortslutter til tilstødende ben.

Bilag F-tjeklisten er en tjekliste over designtiltag til at undgå systematiske fejl. Det omfatter:

- Oversigt over produkter

- Information om ansøgning

- Sikkerhedskoncept

- Livstidsforudsigelser

- FIT

- FMEDA-beregninger - SFF og DC

- Sikkerhedsmekanismer for hardware

- Beskrivelse af diagnostik

- EMC robusthed

- Drift i redundante konfigurationer

- Bilag og dokumentliste

Sammenfattende er den funktionelle sikkerhedscertificering for en nyligt introduceret komponent via Route 1S lang, kompleks, tidskrævende, intens og omfattende. Heldigvis er Route 2S, som nævnt ovenfor, en alternativ tilgang, der er levedygtig for nogle komponenter.

Rute 2S: En alternativ vej

Den vej, der er kendt som rute 2S, kan anvendes til en frigivet del med felterfaring og data og betegnes som "gennemprøvet i brug". Det er baseret på en analyse af kundernes returneringer og antallet af leverede enheder. Den kan ikke bruges med nye dele, som har ringe eller ingen "track record" for eksponering i faktisk brug.

Route 2S tillader SIL-certificering, som om delen var fuldt analyseret i henhold til IEC 61508-standarden. Det er tilgængeligt for modul- og systemdesignere, hvis de tidligere har brugt den pågældende IC med succes og kender fejlprocenten fra felten. De indbyggede test- og verifikationsfunktioner gør sammen med ydelsesdata AD7214-4 og AD7214-8 til gode kandidater til Route 2S.

At anvende Route 2S kræver detaljerede og statistisk signifikante data om returneringer og fejl i marken. Dette krav er meget sværere at opfylde for IC-leverandører, end det er for kort- eller modulleverandører. Årsagen er, at førstnævnte generelt ikke har tilstrækkelig viden om den endelige anvendelse, eller hvor stor en procentdel af de fejlbehæftede enheder fra marken, der returneres til dem til analyse.

Konklusion

Route 1S-vejen til funktionelt sikker certificering af nye produkter er grundig, omfattende og detaljeret. Det er også teknisk udfordrende og bestemt tidskrævende. I modsætning hertil gør Route 2S-processen det muligt at certificere frigivne produkter baseret på felterfaringer, fejl og analysedata. Dette er en nyttig rute, som understøttes af RTD-interface-IC'erne AD7214-4 og AD7214-8, da de har den nødvendige historik. Lige så vigtigt er det, at disse IC'er indeholder mange diagnostiske og selvtestende funktioner og egenskaber, der gør dem til egnede kandidater til en sådan certificering.

Relateret indhold

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.