Forstå og minimer effekten af jitter på højhastighedsforbindelser

Bidraget af DigiKeys nordamerikanske redaktører

2023-12-21

Clock-oscillatorer leverer timing-hjerteslag for moderne kredsløb ved at pace systemkomponenter. Efterhånden som systemhastighederne stiger til flere hundrede megahertz (MHz) og højere, skal disse clock-signaler være hurtigere og give meget lav jitter, typisk under 100 femtosekunder (fs), for at opretholde systemets ydeevne. De skal også opretholde deres lave jitter-specifikationer over tid på trods af variationer i temperatur og spænding.

Noget jitter skyldes signalvejsstøj og forvrængning, og det kan reduceres noget ved hjælp af reclocking- og retiming-teknikker. Jitter genereres dog også af clock-kilden, som normalt er en oscillator. Det skyldes forskellige fysiske fænomener, herunder termisk støj, procesfejl, støj fra strømforsyningen, anden ekstern støj, der trænger ind i clock-oscillatoren, materialespændinger og mange andre subtile faktorer. Uanset kilden er det op til designeren at gøre alt, hvad der er muligt, for at minimere den indbyggede clock-jitter, da manglerne ikke er reversible.

Denne artikel diskuterer jitter-problemer fra forskellige perspektiver. Derefter introduceres forskellige clock-oscillatorer fra Abracon LLC, og det vises, hvordan jitter kan minimeres ved at tilpasse clock-oscillatorens ydeevne til applikationen.

Grundlæggende om jitter

Clock-jitter er afvigelsen af en clock-kant fra dens ideelle position i tiden. Denne jitter påvirker timingpræcisionen og nøjagtigheden af transmissionen af datasignaler, som klokkesignalet styrer, hvilket fører til en forringelse af signal-støj-forholdet (SNR) i modtagerens dekodnings-/demodulationskredsløb eller andre system-IC'er. Det resulterer i en højere bitfejlsrate (BER), flere retransmissioner og reduceret effektiv datagennemstrømning.

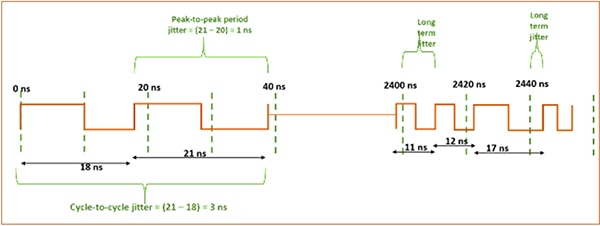

Da clock-jitter er kritisk, analyseres det i vid udstrækning i systemer, der sender et signal fra en sendekilde til en modtager via kabler, stik eller printkort. Afhængigt af anvendelsen kan den karakteriseres på mange måder, herunder cyklus-til-cyklus, periode og langtidsjitter (figur 1).

Figur 1: Begrebet "jitter" dækker over mange variationer i timingen, herunder cyklus-til-cyklus-jitter, periode-jitter og langtids-jitter. (Billedkilde: VLSI Universe)

Figur 1: Begrebet "jitter" dækker over mange variationer i timingen, herunder cyklus-til-cyklus-jitter, periode-jitter og langtids-jitter. (Billedkilde: VLSI Universe)

- Cyklus-til-cyklus-jitter betyder ændringen i clock-perioden over to på hinanden følgende cyklusser og er ikke relateret til frekvensvariation over tid.

- Periodejitter er afvigelsen af en clock-periode i forhold til dens middelperiode. Det er forskellen mellem den ideelle og den faktiske clock-periode, og kan specificeres som enten RMS (root-mean-square) periodejitter eller peak-til-peak periodejitter.

- Langtidsjitter er clock-kantens afvigelse fra den ideelle position over en længere periode. Det svarer lidt til drift.

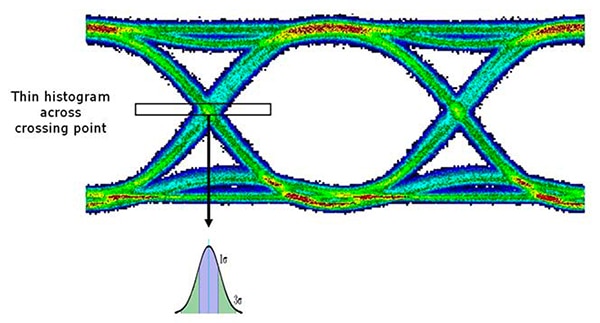

Jitter kan ødelægge den timing, der bruges af andre underfunktioner, komponenter eller systemer, der bruges til at opnå datagendannelse med lav BER, eller tempokomponenter som hukommelseselementer eller processorer i et synkront system. Det ses i øjendiagrammet i figur 2 som en udvidelse af crossover-punktet i bittimingen.

Figur 2: I et øjendiagram ses jitter som en udvidelse af det kritiske timing-crossover-punkt i datastrømmen. (Billedkilde: Kevin K. Gifford/Univ. of Colorado)

Figur 2: I et øjendiagram ses jitter som en udvidelse af det kritiske timing-crossover-punkt i datastrømmen. (Billedkilde: Kevin K. Gifford/Univ. of Colorado)

Ved serielle datalinks skal kredsløbet i den modtagende ende forsøge at genetablere sin egen clock for at opnå optimal afkodning af datastrømmen. For at gøre det skal den synkronisere og låse sig fast på kilde-clocken, ofte ved hjælp af en PLL (phase lock loop). Jitter påvirker systemets evne til at gøre dette præcist, hvilket kompromitterer dets evne til at gendanne data med en lav BER.

Bemærk, at jitter kan måles i både tids- og frekvensdomænet; begge er lige gyldige perspektiver på det samme fænomen. Fasestøj er en frekvensdomineret visning af støjspektret omkring oscillatorsignalet, mens jitter er en tidsdomineret måling af oscillatorperiodens timingnøjagtighed.

Jitter-målinger kan udtrykkes på flere måder. Det angives ofte ved hjælp af tidsenheder som "jitter på 10 picosekunder" (ps). RMS (Root mean square) fasejitter er en tidsdomæneparameter, der er afledt af fasestøjsmålingen (frekvensdomænet). Jitter kaldes nogle gange også fasejitter, hvilket kan være forvirrende, men det er stadig en jitterparameter i tidsdomænet.

Efterhånden som linkets driftsfrekvenser og deres clocks stiger fra nogle få tiendedele MHz til flere hundrede MHz og højere, falder den tilladte jitter på clock-kilden til omkring 100 fs eller mindre. Disse frekvenser gælder for optiske moduler, cloud-computing, netværk og højhastigheds Ethernet, som alle er funktioner og applikationer, der kræver en bærefrekvens mellem 100 og 212/215 MHz og datahastigheder på op til 400 gigabit pr. sekund (Gbps).

Håndtering af krystalen

Den mest almindelige måde at skabe et stabilt, ensartet og præcist clock-signal på er at bruge en kvartskrystaloscillator. Et tilhørende oscillatorkredsløb understøtter krystallen. Der er mange sådanne kredsløbsfamilier, hver med forskellige kompromiser. Krystaller er blevet brugt i denne rolle siden 1930'erne til trådløs radiokommunikation i de mellemfrekvente (300 kilohertz (kHz) til 3 MHz) og højfrekvente (3 til 30 MHz) RF-bånd.

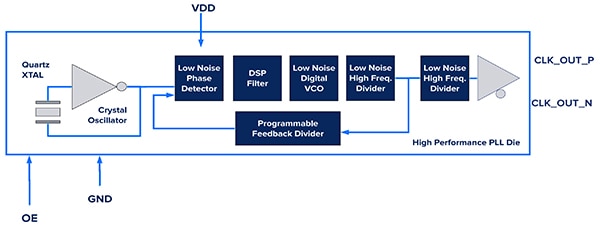

En udbredt metode til at generere clocks med lav jitter er at bruge en af de mange variationer af PLL-baserede arkitekturer. For eksempel kommer enheder i Abracons AX5- og AX7 ClearClock™-familier i henholdsvis 5 × 3,2 millimeter (mm) og 5 × 7 mm pakker og bruger en sofistikeret PLL-teknologi til fremragende lav jitter-ydelse (figur 3).

Figur 3: Abracon AX5 og AX7 clock-oscillatorer bruger et af de mange PLL-baserede designs, men med subtile forbedringer for at minimere jitter. (Billedkilde: Abracon)

Figur 3: Abracon AX5 og AX7 clock-oscillatorer bruger et af de mange PLL-baserede designs, men med subtile forbedringer for at minimere jitter. (Billedkilde: Abracon)

Sammen med driftsfrekvens og oscillatordesign påvirkes jitter-ydelsen af den fysiske størrelse af kvartskrystallen i oscillatorkernen. Efterhånden som størrelsen på denne krystal reduceres, bliver det mere udfordrende at levere overlegen RMS-jitterydelse.

For clocking-løsninger i 100 til 200 MHz-båndet og i mindre formfaktorer end de PLL-baserede AX5- og AX7-enheder er der brug for en ny oscillatorarkitektur. Disse krav til mindre størrelser er typisk forbundet med den seneste generation af optiske transceivere og moduler. Der er fire etablerede måder at designe en clock-oscillator på i området 100 til 200 MHz:

- Brug en kvartsoscillator med en inverteret mesakvarts som resonatorelement.

- Brug en kvartsoscillator med et kvartsemne med tredje overtoner som resonatorelement.

- Brug en oscillatorsløjfe baseret på en sub-50 MHz, tredje overtone/fundamental-mode kvartsblank, eller en sub-50 MHz, temperaturkompenseret krystaloscillator parret med en heltals- eller fraktional-mode PLL-IC.

- Brug et mikroelektromekanisk system (MEMS) med en resonatorbaseret oscillatorsløjfe på under 50 MHz parret med en PLL-IC med en heltals- eller brøkdelstilstand.

Mulighed 1 giver ikke den bedste RMS-jitterydelse, og det er heller ikke den mest omkostningseffektive løsning. Mulighed 3 bliver kompliceret og har præstationsmangler, mens MEMS-resonatormetoden i mulighed 4 ikke opfylder de primære præstationskriterier på 200 fs maksimal RMS-jitter. I modsætning hertil bruger mulighed 2 et optimalt designet kvartsemne med tredje overtone, hvor der tages hensyn til elektrodernes geometri og optimering af skærevinklen. Denne kombination er optimal med hensyn til pris, ydeevne og størrelse.

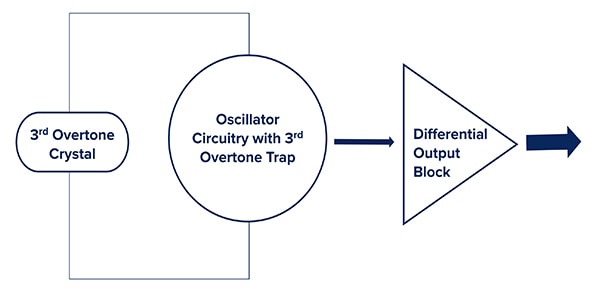

Ved hjælp af denne tilgang udviklede Abracon ClearClock-løsninger med "tredje overtone" (figur 4). Disse enheder bruger en mere støjsvag arkitektur til at muliggøre fremragende, ultra-lav RMS-jitterydelse og ekstrem energieffektivitet i miniaturepakker så små som 2,5 × 2,0 x 1,0 mm.

Figur 4: Den "tredje overtone" ClearClock-løsning fra Abracon bruger en mere støjsvag arkitektur til at forbedre den samlede ydeevne og energieffektivitet. (Billedkilde: Abracon)

Figur 4: Den "tredje overtone" ClearClock-løsning fra Abracon bruger en mere støjsvag arkitektur til at forbedre den samlede ydeevne og energieffektivitet. (Billedkilde: Abracon)

I dette system sikrer omhyggeligt design af krystalemnet med tredje overtoner sammen med korrekt filtrering og "trapping" af det ønskede bæresignal en fremragende RMS-jitterydelse ved de ønskede bærefrekvenser.

Denne arkitektur bruger ikke en typisk PLL-tilgang, så der er ingen opkonvertering. Derfor er der ikke behov for standard PLL-brøk eller heltalsmultiplikation, og den endelige udgangsfrekvens har en en-til-en-korrelation med resonansfrekvensen for kvartskrystallen med tredje overtone. Fraværet af brøk- eller heltalsmultiplikation forenkler designet og muliggør minimal jitter i den mindst mulige størrelse.

Specifikationer og ydeevne i virkeligheden

Clock-oscillatorer er mere end bare et krystal og dets analoge kredsløb. De inkluderer buffering for at sikre, at oscillatorens udgangsbelastning og dens kort- og langsigtede variationer ikke påvirker enhedens ydeevne. De understøtter også forskellige differentierede digitale logiske udgangsniveauer for kredsløbskompatibilitet. Denne kompatibilitet fjerner behovet for en ekstern IC til oversættelse af logikniveau. En sådan IC ville øge omkostningerne, fodaftryk og jitter.

Da clock-oscillatorer bruges i så mange forskellige applikationer med forskellige skinnespændinger, skal de tilbydes i en række forskellige forsyningsspændinger som +1,8 volt, +2,5 volt eller +3,3 volt samt brugerdefinerede værdier, der typisk spænder fra 2,25 til 3,63 volt. De skal også kunne fås med forskellige output-formater, såsom lavspændings-positiv/pseudo-emitterkoblet logik (LVPECL) og lavspændings-differentialsignalering (LVDS), samt andre formater.

Et kig på to familier af krystalclock-oscillatorer, AK2A og AK3A, viser, hvad der kan opnås gennem sofistikeret forståelse og integration af materialer, design, arkitektur og test. De to familier ligner hinanden, og de mest markante forskelle er størrelsen og den maksimale frekvens.

AK2A-familien: Denne familie af krystaloscillatorer tilbydes ved nominelle frekvenser fra 100 til 200 MHz og fås med driftsspændinger på 2,5 volt, 3,3 volt og 2,25 til 3,63 volt med LVPECL-, LVDS- og HCSL-differentialudgangslogik.

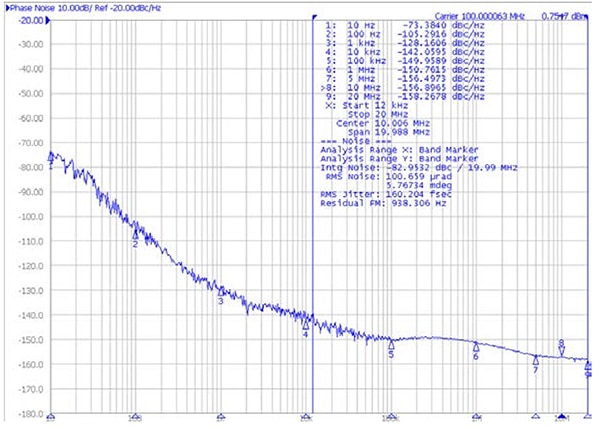

Alle familiemedlemmer har samme ydeevne, herunder lav RMS-jitter. For eksempel er AK2ADDF1-100.000T en 100,00 MHz, 3,3 volt enhed med LVDS-udgange og en RMS-jitter på 160,2 fs (figur 5). Dens frekvensstabilitet er fremragende med bedre end ±15 ppm (parts per million) over temperatur, og den leveres i en seksledet SMD-pakke (surface mount device), der måler 2,5 × 2,0 × 1,0 mm.

Figur 5: Jitter er vist til at være 160 fs for AK2ADDF1-100.000T, en 3,3 volt, 100 MHz enhed med LVDS-udgange. (Billedkilde: Abracon)

Figur 5: Jitter er vist til at være 160 fs for AK2ADDF1-100.000T, en 3,3 volt, 100 MHz enhed med LVDS-udgange. (Billedkilde: Abracon)

Men når clock-frekvenserne stiger, skal jitteren mindskes for at opretholde ydeevnen på systemniveau. For AK2ADDF1-156.2500T, en 156,25 MHz LVDS-oscillator, falder den typiske RMS-jitter til 83 fs.

AK3A-familien: Enhederne i AK3A-familien er lidt større end dem i AK2A-familien med et fodaftryk på 3,2 × 2,5 × 1,0 mm (figur 6). Versioner er tilgængelige og specificeret til 212,5 MHz, hvilket er noget højere end 200 MHz-grænsen for AK2A-familien.

Figur 6: AK3A-krystaloscillatorerne (til højre) er lidt længere og bredere end AK2A-serien (til venstre); der findes versioner til frekvenser på op til 212,5 MHz, sammenlignet med 200 MHz for AK2A. (Billedkilde: Abracon)

Figur 6: AK3A-krystaloscillatorerne (til højre) er lidt længere og bredere end AK2A-serien (til venstre); der findes versioner til frekvenser på op til 212,5 MHz, sammenlignet med 200 MHz for AK2A. (Billedkilde: Abracon)

De overordnede specifikationer for denne AK3A-enhed svarer til dem for det tilsvarende AK2A-familiemedlem. Et eksempel er AK3ADDF1-156.2500T3, en 156,25 MHz LVDS-oscillator, der har en typisk RMS-jitter på 81 fs, hvilket er lidt bedre end det tilsvarende medlem af AK2A-familien.

Jitter for begge familier varierer afhængigt af driftsfrekvens, driftsspænding, pakkestørrelse og valg af udgange.

Yderligere overvejelser fra den virkelige verden

Det er ikke nok at have en clock-oscillator, der kun lever op til specifikationerne den dag, den forlader fabrikken. Som med alle komponenter, især analoge og passive komponenter, er disse oscillatorer udsat for drift over tid på grund af ældning af de indgående materialer og interne spændinger.

Denne virkelighed er især en udfordring for højtydende clock-oscillatorer, da der ikke er nogen bekvemme eller enkle måder at korrigere eller kompensere for denne drift ved at tilføje software eller smarte kredsløb. Der er dog nogle måder at afbøde virkningerne af afdrift på. Disse omfatter lange perioder med burn-in hos slutbrugeren for at fremskynde oscillatorens ældning eller brug af en temperaturstabiliseret oscillator i et ovnstyret kabinet. Førstnævnte er tidskrævende og en udfordring for forsyningskæden, mens sidstnævnte er stor, dyr og strømkrævende.

I erkendelse af, at ældning er en kritisk parameter, tilbyder Abracons ClearClock-familie en stringent, altomfattende frekvensnøjagtighed i hele slutproduktets levetid på 10 til 20 år. Abracon sikrer overholdelse af frekvensstabilitet på bedre end ±50 ppm i denne periode. Dette opnås ved omhyggelig udvælgelse og fremstilling af tredje-overtonekrystallen og konditionering af den, så den opfylder ±15 ppm stabilitet over -20 °C til +70 °C og ±25 ppm stabilitet over -40 °C til +85 °C.

Som altid handler ingeniørarbejde om kompromiser. Abracon AK2A- og AK3A-serierne giver forbedret jitter-støj-ydelse sammenlignet med deres forgængere (henholdsvis Gen I AK2 og AX3) ved at bruge en næstegenerations (Gen II) oscillator-ASIC, hvilket sikrer ultra-lav RMS-jitter-ydelse.

Denne forbedring er opnået på bekostning af en lille stigning i strømforbruget. Det maksimale strømforbrug stiger fra 50 milliampere (mA) for Gen I til 60 mA for Gen II, selvom lavspændingsenhederne kører med omkring halvdelen af denne værdi. Anden generation af ClearClock-oscillatorer giver derfor ultra-lav RMS-jitter, mens de stadig har et lavt strømforbrug.

Konklusion

Timing-oscillatorer er hjertet i et datalink eller en clocking-funktion, og deres nøjagtighed, jitter og stabilitet er kritiske parametre for at opnå den krævede ydelse på systemniveau, herunder høj SNR og lav BER. Højere clock-frekvenser kan opnås med innovative materialevalg og arkitekturer, der opfylder de strenge ydelsesspecifikationer, som industrien og dens forskellige standarder kræver. Abracon AK2A- og AK3A-serierne har en jitter på under 100 fs i området 100 til 200 MHz i SMD-pakker, der kun måler et par millimeter på hver side.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.