Grundlæggende om frekvenssynthesizere med låst fasesløjfe

Bidraget af DigiKeys nordamerikanske redaktører

2021-02-03

Stigende datahastigheder i højhastigheds serielle kommunikationsbusser kræver en systemclock med højere frekvenser, overlegen stabilitet, større frekvensopløsning og højere signalrenhed. Direkte digitale synthesizere tilbyder disse egenskaber, men kun ved frekvenser under 2 eller 3 gigahertz (GHz). En løsning er påkrævet for frekvenser på op til snesevis af gigahertz.

Denne løsning begynder med fase-låste (PLL) -baserede analoge frekvenssynthesizere, der genererer clock-frekvenser op til 30 GHz. Derefter anvender heltals N-synthesizere (som multiplicerer referencefrekvensen med en heltal) og brøkdelte N-synthesizers (som multiplicerer referencefrekvensen med ikke-heltal fraktionerede værdier) specielle teknikker, der minimerer fasestøj og lignende signalurenheder.

Denne artikel beskriver designet af både heltal og brøk N-frekvenssynthesizere ved hjælp af eksempler på enheder fra Analog Devices. Artiklen fremhæver også de innovationer, der gør det muligt at bruge disse enheder til højhastigheds serielle datalinks såvel som til frekvente agile radarer.

Heltals N-faselåste loop-synthesizere

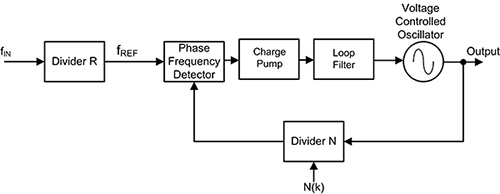

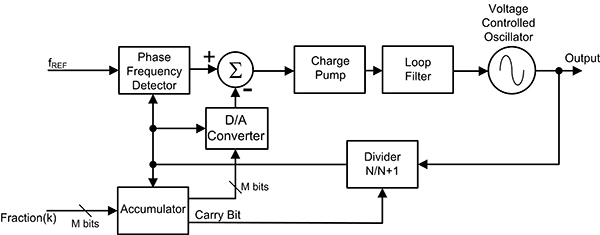

PLL-kredsløb bruges til frekvens- og fasestyring. De kan konfigureres som clock-kilder, frekvensmultiplikatorer, demodulatorer, trackking-generatorer eller clock-gendannelseskredsløb. Hver af disse applikationer kræver forskellige egenskaber, men de bruger alle det samme grundlæggende kredsløbskoncept. Figur 1 viser et blokdiagram over en grundlæggende PLL konfigureret som en frekvensmultiplikator.

Figur 1: Blokdiagram over et klassisk heltal N-fase frekvenssynthesizer med fastlåst loop. (Billedkilde: DigiKey)

Figur 1: Blokdiagram over et klassisk heltal N-fase frekvenssynthesizer med fastlåst loop. (Billedkilde: DigiKey)

Driften af dette kredsløb er typisk for alle faselåste loops. Det er dybest set et feedbackkontrolsystem, der styrer fasen i en spændingsstyret oscillator (VCO). Indgangssignalet påføres en for-skaleringsdeler, der deler indgangsfrekvensen med en faktor R. Udgangen fra forskaleren er referencefrekvensen, som danner en indgang af en fasefrekvensdetektor (PFD).

Den anden PFD-indgang er et tilbagemeldingssignal fra udgangen fra en divide-by-N-tæller. Normalt, hvis PLL er låst, vil frekvenserne af begge signaler være næsten de samme. Fasedetektorens output er en spænding, der er proportional med faseforskellen mellem de to indgange. Hvis loopen er låst op, som det sker ved opstart, eller hvis der er et stort øjeblikkeligt skift i inputfrekvensen, benyttes fasefrekvensdetektoren til at styre PLL-driftsfrekvensen til den ønskede indstilling. Når denne frekvens er opnået, vender PFD tilbage til fasedetektortilstand og har et output, der er proportionalt med faseforskellen mellem referencefrekvensen og feedback-signalet.

Fasefrekvensdetektoren driver en ladepumpe, som er en bipolar koblet strømkilde. Dette betyder, at det kan afgive positive og negative strømimpulser til loop-filteret på PLL.

Sløjfefilteret udjævner fasefejlsignalet og bestemmer også PLL's dynamiske karakteristika. Det filtrerede signal styrer VCO. Bemærk, at udgangen af VCO er ved en frekvens, der er N gange den indgang, der leveres til frekvensreferenceindgangen til fasefrekvensdetektoren, og er N/R gange frekvensindgangen. Dette udgangssignal sendes tilbage til fasedetektoren via divideret med N-tælleren.

Normalt er sløjfefilteret designet til at matche de egenskaber, der kræves ved anvendelse af PLL. Hvis PLL skal erhverve og trackke et signal, vil båndbredden af sløjfefilteret være større, end hvis den forventede en fast indgangsfrekvens. Frekvensområdet, som PLL vil acceptere og låse fast på, kaldes "indfangningsområde". Når PLL er låst og trackker et signal, kaldes frekvensområdet, som PLL følger, "tracking range". Generelt er trackking-området større end indfangningsområdet. PLL-sløjfefilteret bestemmer også, hvor hurtigt signalfrekvensen kan ændre sig og stadig opretholde lås - dvs. den maksimale svinghastighed. Jo smallere sløjfefilterets båndbredde, jo mindre er den opnåelige fasefejl. Dette kommer på bekostning af langsommere respons og reduceret optagelsesområde. PLL'er, der anvendes i clock-applikationer, fungerer primært ved faste frekvenser. Generelt skal båndbredden af sløjfefilteret være meget mindre end referencefrekvensen.

Da PLL-udgangsfrekvensen er et helt talmultipel af referencefrekvensen, er dens frekvensopløsning lig med referencefrekvensen. At opnå en finere frekvensopløsning kræver nedsættelse af referencefrekvensen, hvilket gøres med tælleren R.

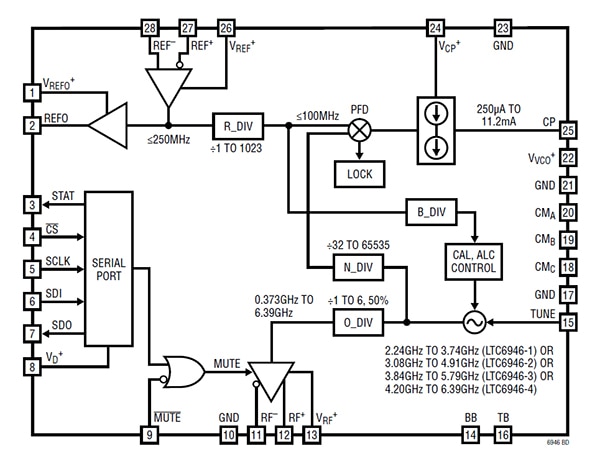

Et kommercielt eksempel på et helt N-frekvenssynthesizer er Analog Devices' LTC6946IUFD-3#PBF, en støjsvag 0,64 til 5,790 GHz synthesizer med en integreret VCO og fremragende præstationer (figur 2). Det er medlem af en familie på fire synthesizer-IC'er, hver med et forskelligt frekvensområde, der dækker et samlet interval på 0,373 til 6,390 GHz.

Figur 2: Blokdiagrammet for de Analog Devices LTC6946IUFD-3 # PBF-heltal N-frekvenssynthesizer med integreret VCO. (Billedkilde: Analog Devices)

Figur 2: Blokdiagrammet for de Analog Devices LTC6946IUFD-3 # PBF-heltal N-frekvenssynthesizer med integreret VCO. (Billedkilde: Analog Devices)

Denne synthesizer kræver et eksternt brugerforsynet sløjfefilter, som kan optimeres til den specifikke applikation. Der er en intern tæller med forudskala med et skilleområde fra 1 til 1023. Sløjfedeleren har et interval fra 32 til 65535. Opladningspumpens strøm kan justeres fra 250 mikroampere (mA) til 11,2 millimeter (mA), så den passer til kravene i sløjfefilteret.

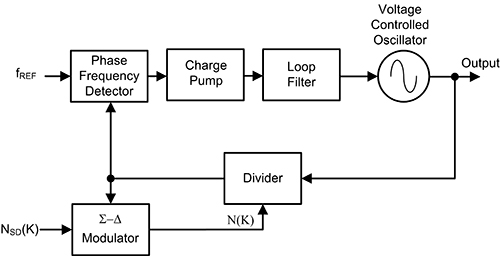

Fraktioneret N-fase låst sløjfe synthesizers

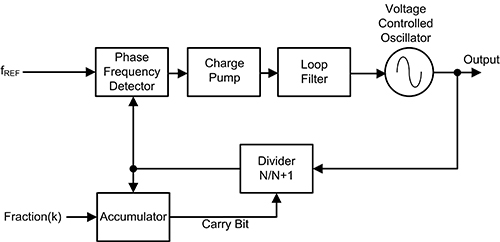

Frekvensopløsningen af PLL-synthesizeren kan forbedres ved at reducere trinstørrelsen til mindre end heltalværdier - dvs. lave fraktionerede trin i sløjfe-skillelinjen (N). Dette opnås ved dynamisk at variere eller "fordele" nedtællingsværdien. Dette betyder, at skilleindstillingen holder værdien N i et fast antal cyklusser af PLL-udgangsfrekvensen og trinvis trækkes til en anden værdi, såsom N + 1. For eksempel, hvis skilleindstillingen er 4 for tre referenceperioder og 5 for den fjerde referencecyklus, er den effektive nedtælling 4,25. En måde at opnå dette på er at bruge en akkumulator som vist i figur 3.

Figur 3: Blokdiagrammet for en fraktioneret N PLL-synthesizer ved hjælp af en akkumulator til at modulere skilletællingen. (Billedkilde: DigiKey)

Figur 3: Blokdiagrammet for en fraktioneret N PLL-synthesizer ved hjælp af en akkumulator til at modulere skilletællingen. (Billedkilde: DigiKey)

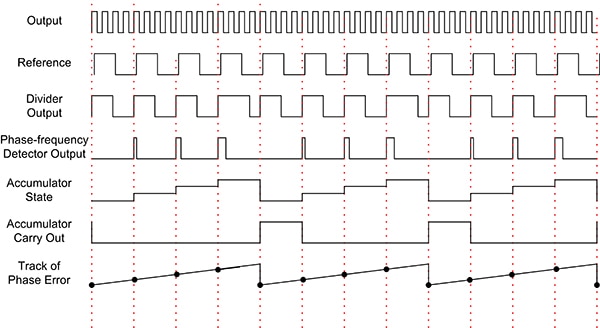

Akkumulatoren tæller outputimpulser fra opdeleren, og hver M, hvor M er akkumulatorens modul, udsender den en bærebit, der ændrer opdelingsindgangen. Figur 4 fortsætter eksemplet med at indstille en brøkdelerindstilling på 4,25.

Figur 4: Timingsdiagram for en brøkdel N-synthesizer ved hjælp af en akkumulator. (Billedkilde: DigiKey)

Figur 4: Timingsdiagram for en brøkdel N-synthesizer ved hjælp af en akkumulator. (Billedkilde: DigiKey)

Akkumulatoren drives af den delte output og tæller modulo fire, dvs. M er lig med fire. Hver fjerde puls genererer den en bæreoutput, der forøger skilletællingen med en. Akkumulatoren nulstilles og begynder at tælle igen. Stigningen i skilleindstillingen skifter outputfrekvensen, hvilket resulterer i en akkumuleret faseforskydningsfejl. Trackking af fasefejl viser pulsværdien som en funktion af tiden.

Den gennemsnitlige skilleindstilling er 4,25, men synthesizer-output er fasemoduleret, hvilket resulterer i uønskede toner i output. Når man ser på akkumulatortilstanden, er det tydeligt, at den tracker fasefejlen. Dette kan bruges til at fjerne moduleringen som vist i figur 5.

Figur 5: Brug af D/A-konverteret akkumulatortilstand til at annullere fasemodulationen på grund af den fraktionerede N-dithering. (Billedkilde: DigiKey)

Figur 5: Brug af D/A-konverteret akkumulatortilstand til at annullere fasemodulationen på grund af den fraktionerede N-dithering. (Billedkilde: DigiKey)

Akkumulatortilstanden konverteres til analog ved hjælp af en digital-til-analog (D/A) konverter og skaleres og trækkes fra fasefrekvensdetektoroutputtet for at annullere fasemodulationen på grund af den fraktionerede N-dithering. Dette skal gøres med stor omhu; hvis korrektionssignalet ikke nøjagtigt matcher fasefejlen, vil uønskede toner ved udgangen forekomme.

Indtast sigma-delta-modulatoren

Periodiciteten i akkumulatoren er årsagen til uønsket output fra synthesizeren. Hvis akkumulatoren erstattes af en sigma-delta-modulator, kan digitale teknikker anvendes til at modulere skilletallet på en måde for at minimere uønskede svar og støj. Denne udskiftning er vist i figur 6.

Figur 6: Udskiftning af akkumulatoren med en sigma-delta-modulator muliggør, at digitale teknikker kan anvendes til at variere divideretallet for at reducere uønskede svar. (Billedkilde: DigiKey)

Figur 6: Udskiftning af akkumulatoren med en sigma-delta-modulator muliggør, at digitale teknikker kan anvendes til at variere divideretallet for at reducere uønskede svar. (Billedkilde: DigiKey)

Der er virkelig to almindelige digitale teknikker, der anvendes i sigma-delta-moduleringstopologien. Den første involverer at øge antallet af N-skilletællinger over et bredere interval af værdier, således at den gennemsnitlige delingsfaktor vil producere den ønskede brøkdelingsværdi. Dette vil reducere de primære fraktionerede spor. Den akkumulatorbaserede synthesizer varierer antallet af to tilstande. Dette er en første ordens moduleringsmetode. En n-ordens sigma-delta fraktioneret PLL modulerer N-tælleren mellem 2n forskellige værdier. For eksempel vil en tredje ordens modulator skifte mellem otte forskellige skilleværdier, og en fjerde ordens modulator skifte mellem 16 forskellige skilleværdier.

Den anden digitale teknik, også kaldet dithering, involverer randomisering af 2N sekvens, så det er pseudorandom. Mens der stadig opretholdes et gennemsnitligt brøkdelingsforhold, konverterer det fraktionerede spor til formet tilfældig støj på en sådan måde, at det kan filtreres af PLL.

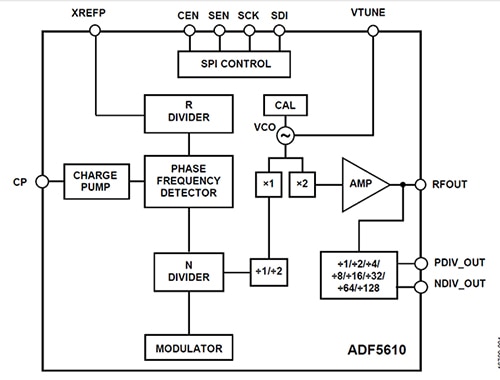

En kommerciel version af en sigma-delta fraktioneret N-synthesizer er Analog Devices ADF5610BCCZ, en støjsvag 0,57 megahertz (MHz) til 14,6 GHz fraktioneret N-synthesizer med en integreret VCO (figur 7).

Figur 7: Et blokdiagram over de Analog Devices ADF5610BCCZ, som understøtter både brøkdel N eller heltal synthesizerkonfigurationer. (Billedkilde: Analog Devices)

Figur 7: Et blokdiagram over de Analog Devices ADF5610BCCZ, som understøtter både brøkdel N eller heltal synthesizerkonfigurationer. (Billedkilde: Analog Devices)

ADF5610 kræver en ekstern referenceoscillator og et sløjfefilter. Den har en integreret VCO med en grundlæggende frekvens på 3650 MHz til 7300 MHz. Disse frekvenser fordobles internt og dirigeres til RFOUT-stiften. Der er en differentiel udgang, der gør det muligt at dividere den fordoblede VCO-frekvens med faktorer på 1, 2, 4, 8, 16, 32, 64 eller 128, hvilket gør det muligt at generere RF-udgangsfrekvenser så lave som 57 MHz.

ADF5610 bruger en avanceret sigma-delta-modulator med et 24-bit brøkmodul, der opnår usædvanligt lave uønskede niveauer. Som i alle synthesizere, der bruger en sigma-delta-modulator, bruger denne enhed digitale signalbehandlingsteknikker til at finde det ønskede gennemsnitlige brøkdelingsforhold. Denne proces, er clockket ved PFD-hastigheden, producerer outputmodulationsstøj kaldet kvantiseringsstøj med et højpasfrekvensrespons. Det eksterne lavpas-sløjfefilter bruges til at filtrere denne kvantiseringsstøj til et niveau under fasestøj fra VCO, hvilket forhindrer støj i at bidrage til systemets samlede fasestøj.

ADF5610 inkluderer også en nøjagtig frekvenstilstand for 0 hertz (Hz) frekvensfejl. Denne tilstand er i stand til at generere nøjagtige frekvenser mellem tilstødende heltal N-grænsetrin, mens den stadig bruger det fulde 24-bit faseakkumulatormodul. Det opnår nøjagtige frekvensstrin med en højfasedetektor-sammenligningshastighed, hvilket gør det muligt for PLL at opretholde fremragende fasestøj og uønsket præstationer i denne tilstand.

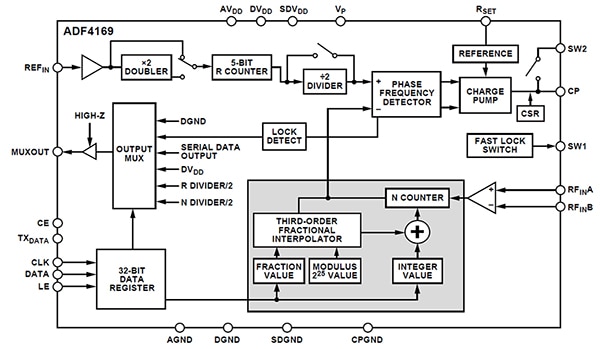

De Analog Devices ADF4169CCPZ-RL7 er en anden PLL-synthesizer, der kan konfigureres som enten et heltal N eller en brøkdel N-enhed. Den fungerer med en RF-båndbredde på op til 13,5 GHz med modulering og bølgeformgenerering. Det bruger en ekstern referencefrekvensindgang, VCO og sløjfefilter. Den har en tredje ordens sigma-delta modulator til fraktioneret N-syntese, der kan deaktiveres, så enheden kan køre i heltal N-tilstand (figur 8).

Figur 8: De Analog Devices ADF4169CCPZ-RL7 bruger en tredjeordens sigma-delta-modulator. (Billedkilde: Analog Devices)

Figur 8: De Analog Devices ADF4169CCPZ-RL7 bruger en tredjeordens sigma-delta-modulator. (Billedkilde: Analog Devices)

ADF4158WCCPZ-RL7-synthesizeren er beregnet til brug i frekvensmodulerede kontinuerlige bølgeradarer (FMCW). Den er i stand til forskellige typer modulerede bølgeformer i frekvensdomænet inklusive savtand og trekantede ramper. Dette er en speciel funktion, der er nødvendig i radarapplikationer.

Konklusion

Stigende datahastigheder i højhastigheds serielle kommunikationsbusser kræver, at designere ser ud over direkte digitale synthesizere, som fungerer bedst under 3 GHz, for systemurløsninger. PLL-baserede frekvenssynthesizere, der bruger heltal N- og brøkdelte N-topologier, giver stabile signaler med lavt støjniveau til højfrekvent clock, seriel datakommunikation og radarapplikationer til frekvenser op til ti gigahertz.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.