Opret hurtigt en højfrekvent clock med lav jitter ved hjælp af et konverteringsloop-modul

Bidraget af DigiKeys nordamerikanske redaktører

2021-08-04

Designere af instrumenterings- og målesystemer har brug for signaler med lavt jitter og uden spuriøse signaler for at kunne levere de signal/støjforhold (SNR) eller fejlvektorstørrelser (EVM), der kræves for at opfylde stadig mere krævende kundekrav. Samtidig er de også udsat for et betydeligt pres for at reducere printpladernes pladsforbrug samt designomkostninger og kompleksitet. Sidstnævnte er afgørende for at forkorte udviklingstiden for at opfylde de stadig kortere time-to-market.

For at imødegå de mange anvendelsesudfordringer er ingeniører nødt til at omstille deres instrumenterings- og måle-clocking-løsninger fra specialfremstillede, traditionelt diskrete designs til mere integrerede løsninger. Et vigtigt skridt i denne retning er at anvende en integreret konverterings-faselåsloop (PLL). Dette gør det muligt at opkonvertere frekvensen af et traditionelt VCO-signal (Voltage-Controlled Oscillator), samtidig med at jitter og fasestøj fra en fast ekstern lokal oscillator (LO) opretholdes i væsentlig grad.

I denne artikel diskuteres den rolle, som konverteringsloop spiller for at opnå branchens laveste integrerede fasestøj. Som eksempel introduceres ADF4401A konverteringsloop system-in-package (TL SiP) fra Analog Devices og viser, hvordan det opfylder kravene til ydeevne gennem et udgangssignal med sub-10 femtosekunder (fs) rms bredbåndsintegreret jitter-kapacitet og forbedret isolation for at dæmpe uønskede komponenter, samtidig med at det opfylder designernes behov for integration, omkostninger, kompleksitet og time-to-market.

Traditionel PLL vs. konverteringsloop-operationer

Det primære formål med et koverteringsloop er at generere et udgangssignal, der er låst til et indgangsreferencesignal med betydeligt reduceret fasestøj inden for båndet, sammenlignet med traditionelle PLL'er.

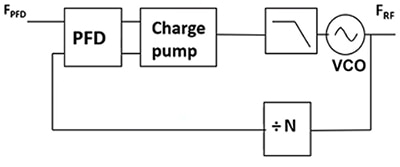

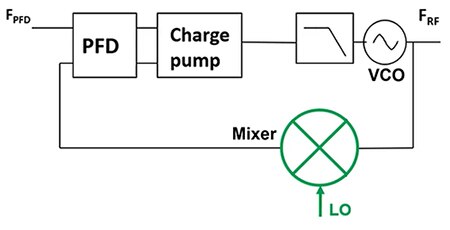

En standard PLL består af et feedback-system, der indeholder en fase-frekvensdetektor (PFD), ladningspumpe, lavpasfilter (LPF), VCO og en feedback-frekvensdeler N (figur 1).

Figur 1: Standard-PLLL'en låser sig til en lavere frekvens (FPFD) og genererer en udgangsfrekvens (FRF). (Billedkilde: Bonnie Baker)

Figur 1: Standard-PLLL'en låser sig til en lavere frekvens (FPFD) og genererer en udgangsfrekvens (FRF). (Billedkilde: Bonnie Baker)

PFD'en sammenligner fasen af input-referencen og fasen af feedback-signalet og genererer en række impulser, der er proportionale med fase-fejlen mellem dem. Ladningspumpen modtager PFD-impulserne og omdanner dem til strømkilde- eller -sinkimpulser, som igen vil korrigere VCO'en op eller ned i frekvens. LPF'en fjerner alle impulsenes højfrekvente energi og konverterer dem til en spænding, som VCO'en kan bruge. VCO'ens udgangssignal føres tilbage til PFD-blokken gennem N-divisoren for at fuldende loopet.

Figur 1's frekvens overførselsfunktion beregnes ved hjælp af ligning 1:

![]() Ligning 1

Ligning 1

Hvor FRF er udgangsfrekvensen

N er forholdet mellem tilbagekoblingsdeleren (kan være heltal eller brøkdel)

FPFD er PFD-frekvensen

Figur 1's grundstøj inden for båndet beregnes ved hjælp af ligning 2:

![]() Ligning 2

Ligning 2

Hvor FOMPLL er PLL'ens fase-grundstøj FOM (Figure Of Merit)

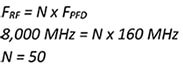

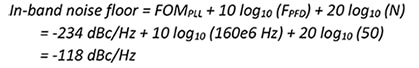

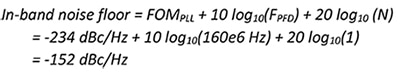

Tag et eksempel med en FOM-værdi for fase-grundstøj i båndet på -234 decibel pr. Hertz (dB/Hz), en PFD-frekvens (FPFD) på 160 megahertz (MHz) og en udgangsfrekvens (FRF) på 8 gigahertz (GHz).

For dette system anvendes ligning 1 til at beregne værdien af N:

Ligning 2 anvendes til at beregne grundstøj inden for båndet:

I ovenstående beregning bidrager N-divisoren kraftigt til det samlede grundstøj inden for båndet med 20 log10 (50), svarende til 34 dB. En mindre N-værdi vil reducere grundstøj inden for båndet, men det vil også reducere udgangsfrekvensen. Så hvordan kan vi generere en høj udgangsfrekvens og samtidig bevare en lavere loop gain (N)?

Figur 2: For en standard-PLLL i dette eksempel har støjen fra feedback-deleren (20 log10(N)) 34 dB højere støj inden for båndet sammenlignet med det nederste gule plot, hvor N = 1. (Billedkilde: Bonnie Baker)

Figur 2: For en standard-PLLL i dette eksempel har støjen fra feedback-deleren (20 log10(N)) 34 dB højere støj inden for båndet sammenlignet med det nederste gule plot, hvor N = 1. (Billedkilde: Bonnie Baker)

Løsningen på dette problem er at erstatte N-deleren med et nedkonverterende mixertrin (figur 3).

Figur 3: Et konverteringsloop bruger en mixer til at nedkonvertere VCO-frekvensen til PFD-frekvensen i stedet for at bruge en traditionel feedbackdeler. (Billedkilde: Bonnie Baker)

Figur 3: Et konverteringsloop bruger en mixer til at nedkonvertere VCO-frekvensen til PFD-frekvensen i stedet for at bruge en traditionel feedbackdeler. (Billedkilde: Bonnie Baker)

I figur 3 erstatter mixeren feedback N-deleren, hvilket resulterer i en loopforstærkning på 1 (N=1). Denne fremgangsmåde vil i høj grad mindske feedback-loopets bidrag til grundstøj inden for båndet. Ved beregningen af støj i båndet er værdien af N nu lig med 1. Ved hjælp af ligning 2 er grundstøj inden for båndet for det modificerede system følgende:

Den nye støj inden for båndet viser en forbedring på 34 dBc/Hz.

I figur 3 er mixeren afhængig af en ekstremt støjsvag LO, kaldet Offset LO. FLO ±FRF skal være lig med FPFD for at opnå låsning.

Med en konverteringsloop-arkitektur er fase-støjen fra Offset LO meget vigtig for at opnå den bedste ydelse ved RF-udgangen. Derfor vil ingeniører typisk konstruere en Offset LO baseret på spændingsstyrede akustiske overfladebølger (SAW), oscillatorer (VCSO'er), kamgeneratorer eller dielektriske resonator-oscillatorer (DRO'er). BEMÆRK: Kontakt Analog Devices for at få hjælp til at designe en Offset LO.

Udfordringer i forbindelse med et konveringsloop

Traditionelt indebærer design af et støjsvag konverteringsloop implementering af mange kredsløbsblokke, hvilket resulterer i et komplekst design, som normalt er stort og med begrænset fleksibilitet. Desuden skal hele kredsløbet valideres og karakteriseres for måloperationen. Et vigtigt designproblem er f.eks. LO-lækage (LO til RF-isolation) til RF-udgangssignalet. Det er en stor udfordring for ingeniørerne at tage fat på. Ved traditionelle konstruktioner foretager ingeniørerne normalt flere gentagelser af konstruktionen for at opnå optimeret ydeevne og passende isolering.

Figur 3 viser, hvordan ADF4401A integrerer de vigtigste kredsløbsblokke for at give en fuldt karakteriseret løsning og fjerne de traditionelt vanskelige områder i forbindelse med ydeevne og isolation i et konverteringsloop-design. Denne programmerbare løsning gør det muligt for ingeniører at opnå optimeret ydeevne ved første forsøg og reducere time-to-market.

Evaluering af ADF4401A

ADF4401A er designet til at hjælpe ingeniører med at reducere time-to-market af højtydende instrumentering ved hjælp af en løsning til frekvensgenererings med en RF-båndbredde på 62,5 MHz til 8 GHz. Ved at bruge en nedkonverterende mixer har ADF4401A meget lav in-band støj med en bredbånds-jitter på ~9 femtosekunder (fs) integreret fra 100 Hz til 100 MHz. Design- og layoutteknikkerne i ADF4401A muliggør et typisk spurious-fri dynamisk område på 90 dBc. En pakkestørrelse på 18 x 18 x 2,018 millimeter (mm) reducerer pladsen på printpladen betydeligt sammenlignet med et traditionelt diskret design.

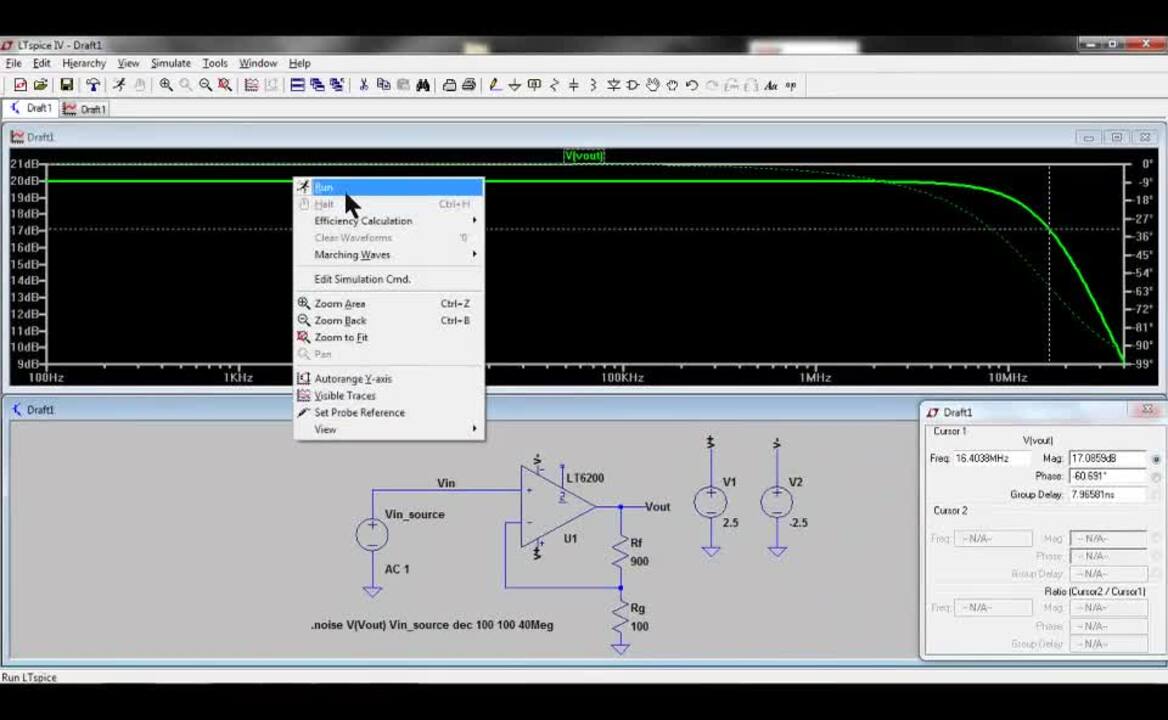

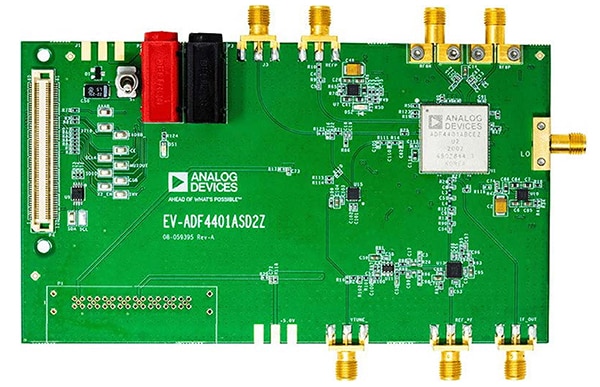

For at evaluere enhedens ydeevne kan designere bruge EV-ADF4401ASD2Z-evalueringskortet (Figur 4). Kortet indeholder et komplet konverteringsloop, herunder en ekstern PFD (HMC3716), et aktivt filter (LT6200) og en multiplexer (ADG1609).

Figur 4: EV-ADF4401ASD2Z-evalueringskortet til ADF4401A konverteringsloop-modulet omfatter en ekstern PFD, et USB-interface og spændingsregulatorer. (Billedkilde: Analog Devices)

Figur 4: EV-ADF4401ASD2Z-evalueringskortet til ADF4401A konverteringsloop-modulet omfatter en ekstern PFD, et USB-interface og spændingsregulatorer. (Billedkilde: Analog Devices)

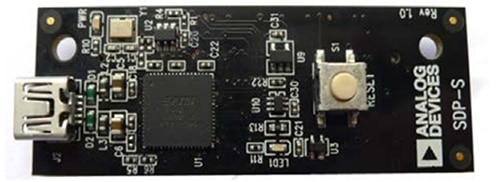

EV-ADF4401ASD2Z indeholder ADF4401A TL SiP med integreret VCO, et loopfilter (5 MHz), et PFD, et USB-interface og spændingsregulatorer. Derudover kræver EV-ADF4401ASD2Z et controllerkort EVAL-SDP-CS1Z (SDP-S) til et system demonstrationsplatform (SDP) (seriel) (Figur 5). Kortet har en USB-forbindelse fra en pc til EV-ADF4401ASD2Z, så den kan programmeres. Styringskortet er ikke inkluderet i EV-ADF4401ASD2Z-sættet.

Figur 5: Et EVAL-SDP-CS1Z (eller SDP-S) controllerkort er påkrævet for at give en USB-forbindelse fra EV-ADF4401ASD2Z til en pc til programmering. (Billedkilde: Analog Devices)

Figur 5: Et EVAL-SDP-CS1Z (eller SDP-S) controllerkort er påkrævet for at give en USB-forbindelse fra EV-ADF4401ASD2Z til en pc til programmering. (Billedkilde: Analog Devices)

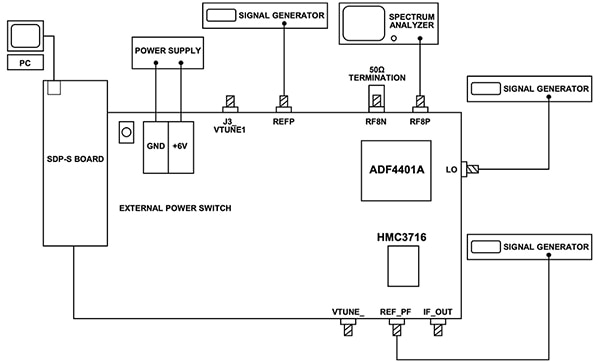

Figur 6 viser de fysiske forbindelser i EV-ADF4401ASD2Z-systemet. Den tilhørende Analysis | Control | Evaluation (ACE) Software styrer TL SiP-funktionerne. Strømmen kommer fra en ekstern 6 volt strømforsyning.

Figur 6: Et EV-ADF4401ASD2Z-opsætningsdiagram viser det udstyr og de forbindelser, der er nødvendige for at evaluere ADF4401A, herunder SDP-S-kontrolkortet, pc, strømforsyning, signalgeneratorer og spektrumanalysator. (Billedkilde: Analog Devices)

Figur 6: Et EV-ADF4401ASD2Z-opsætningsdiagram viser det udstyr og de forbindelser, der er nødvendige for at evaluere ADF4401A, herunder SDP-S-kontrolkortet, pc, strømforsyning, signalgeneratorer og spektrumanalysator. (Billedkilde: Analog Devices)

Det foreslåede udstyr til brug med dette evalueringskort omfatter en Windows-pc, en spektrumanalysator eller en signalkildeanalysator og tre signalgeneratorer.

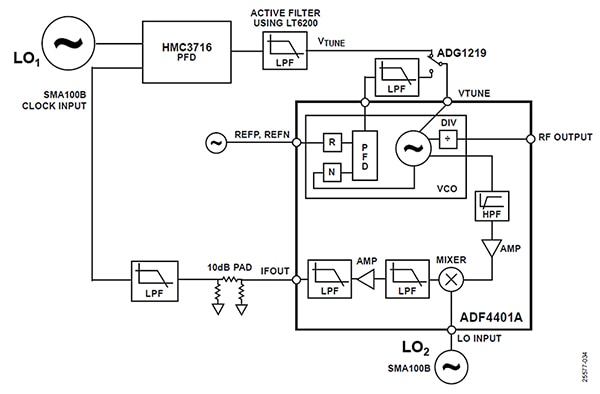

Blokdiagrammet for EV-ADF4401ASD2Z viser ADF4401A-modulet sammen med Analog Devices' HMC3716 PFD, LT6200 op-amp og ADG1219 SPDT-kontakten (figur 7).

Figur 7: EV-ADF4401ASD2Z-evalueringskortets blokdiagram viser de vigtigste komponenter, der understøtter AD4401A-konverteringsloop'et. (Billedkilde: Analog Devices)

Figur 7: EV-ADF4401ASD2Z-evalueringskortets blokdiagram viser de vigtigste komponenter, der understøtter AD4401A-konverteringsloop'et. (Billedkilde: Analog Devices)

Det er vigtigt at bruge en PFD, der kan fungere ved høje frekvenser, da dette minimerer behovet for dividers, som kan forringe støjresponsen inden for båndet. Analog Devices 'HMC3716 fase sammenligning frekvenskapacitet på 1,3 GHz gør den ideel til brug i ADF4401A IF-området. Da et sådant kredsløb kan sammenligne både frekvens og fase, er der ikke længere behov for yderligere kredsløb til at styre frekvensen til den tilsigtede udgangsfrekvens. HMC3716 bliver den eksterne PFD for at fuldføre offset-loop'et. HMC3716's højfrekvente driftsområde og ultralette fase-grundstøj gør det muligt at designe loopfiltre med stor båndbredde.

I figur 7 dæmper LT6200-op-amp med en LPF-konfiguration højfrekvente spurs, mens ADG1219-switchen fuldender systemets konverteringsloop.

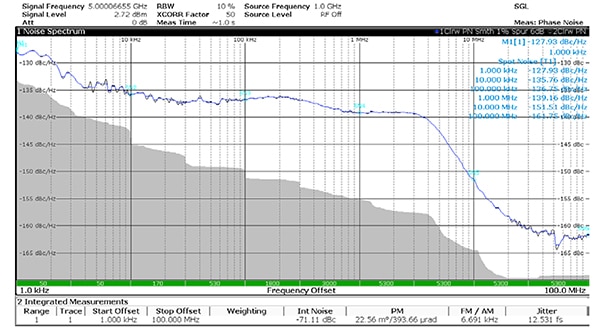

EV-ADF4401ASD2Z-evalueringsudstyret skaber støjplots inden for båndet og jittermålinger som vist i figur 8.

Figur 8: SSB-fasestøj ved 5 GHz output med en ekstern HMC3716-reference på 500 MHz og ekstern LO på 4,5 GHz. (Billedkilde: Analog Devices)

Figur 8: SSB-fasestøj ved 5 GHz output med en ekstern HMC3716-reference på 500 MHz og ekstern LO på 4,5 GHz. (Billedkilde: Analog Devices)

I figur 8 er LO2- og HMC3716-indgangen en SMA100B RF- og mikrobølge signalgenerator. Evalueringskortets LO2-støj inden for båndet er ca. -135 dBc/Hz, hvilket er tydeligt ved lave forskydninger op til 300 kHz. LO2, ADF4401A-modulet, HMC3716 PFD og loopfilteret bidrager til en støj inden for båndet på ca. -140 dBc/Hz. Den interne fasestøj forekommer mellem 5 MHz og 50 MHz, og fase-grundstøj for armaturet er ca. -160 dBc/Hz. Tilsammen giver det en rms-jitter på 12,53 fs i alt.

Konklusion

Instrumenteringssystemer med høj hastighed kræver en lock med ekstrem lav jitter for at sikre, at output-data forbliver ukompromitterede. Udfordringen for ingeniørerne er at finde egnede enheder, der kan opbygge et højhastigheds-system med en gigahertz-clock. ADF4401A konverteringsloop forenkler i høj grad valget af enheder til opbygning af clock-systemet og giver et kompakt modul, der sikrer lav jitter ved højere frekvenser, samtidig med at det reducerer plads på kortet, omkostningerne og time-to-market.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.