Analoge grundlæggende - Del 5: Håndtering af vanskelige problemer med inputstyring til SAR ADC

Bidraget af DigiKeys nordamerikanske redaktører

2020-10-28

Redaktørens bemærkning: Analog-til-digitale konvertere (ADC'er) forbinder den analoge til den digitale verden, og det er således en grundlæggende komponent i ethvert elektronisk system, der forbinder til den virkelige verden. De er også en vigtig afgørende faktor for et systems ydeevne. Denne serie udforsker det grundlæggende i ADC'er, deres forskellige typer og deres anvendelse. Del 1 i denne serie om analoge basics diskuterede SAR ADC'er. Del 2 diskuterer delta-sigma-konvertere. Del 3 ser på pipeline-ADC'er. Del 4 viser, hvordan delta-sigma ADC'er kan generere ultra-støjsvage resultater. Her udforsker del 5 vanskelige problemer med inputstyring for SAR ADC'er.

Mange dataopsamlings-, industriel kontrol- og instrumenteringsapplikationer kræver en ultrahøjhastigheds analog-til-digital-konverter (ADC), når en successiv tilnærmelsesregister (SAR) konverter er perfekt egnet. Det er dog vigtigt at sikre, at det eksterne kredsløb omkring SAR-konverteren også er op til opgaven for at sikre et vellykket konverteringsresultat. De kritiske terminaler, der kræver særlig forsigtighed for SAR-konverteren, er dens analoge signalindgange - hvis de ikke overvåges, kan disse indgangsstifter producere stabilitetsproblemer og kapacitive opladnings "kickbacks", der kan føre til unøjagtige konverteringer og langvarig signaloptagelsestid.

Løsningen til præcis indgangssignalstyring til SAR-konverterapplikationer ligger i kørsel af driftsforstærkere (op-amp). Disse enheder, understøttet af de korrekte outputmodstands- og kondensatorværdier, der er grundlaget for en højpræcisions, robust løsning til højopløsnings-, 16-bit- og 20-bit SAR-konverteringssystemer.

Denne artikel diskuterer kort de problemer, der er forbundet med at opnå stabile og nøjagtige SAR ADC-konverteringer. Derefter introducerer den en passende op-amp til styring af en SAR ADC og viser, hvordan man implementerer de nødvendige input-driverkredsløb. Løsninger fra Analog Devices vil blive brugt som et eksempel.

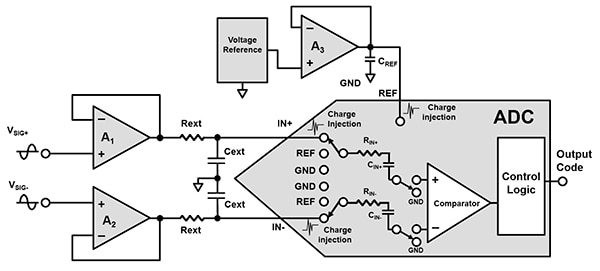

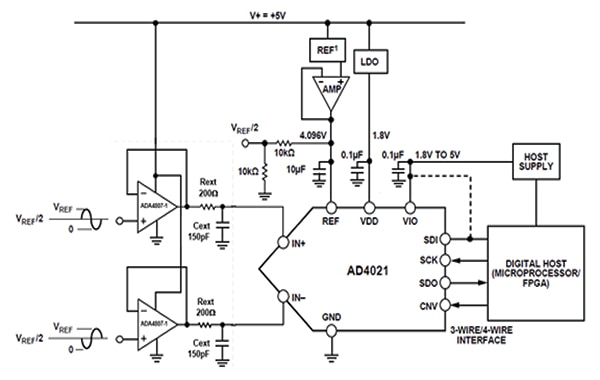

SAR ADC-indgangskredsløb

SAR ADC driver kredsløb har op-AMP (A1 og A2), der adskiller ADC fra deres signalkilder (figur 1). I dette kredsløb holder Rext forstærkeren stabil ved at "isolere" forstærkerens outputtrin fra ADC kapacitiv belastning (CIN+ og CI-) og Cext. Cext og CREF give en næsten perfekt indgangskilde til ADC'en, der absorberer omskiftningsinjektionen fra IN+, IN- og REF-indgangsterminalerne. Indgangsterminalerne (IN+, IN-) sporer indgangssignalets spænding (VSIG+, VSIG-) i løbet af konverterens erhvervelsestid, hvilket giver opladning til ADC's indgangssamplingskondensatorer, CIN+ og CIN-.

Figur 1: I dette kredsløb "isolerer” Rext Cext fra op-ampens udgangstrin. Cext og CREF levere lade-resourcer til den differentielle SAR ADC i prøveudtagningsperioden. (Billedkilde: DigiKey)

Figur 1: I dette kredsløb "isolerer” Rext Cext fra op-ampens udgangstrin. Cext og CREF levere lade-resourcer til den differentielle SAR ADC i prøveudtagningsperioden. (Billedkilde: DigiKey)

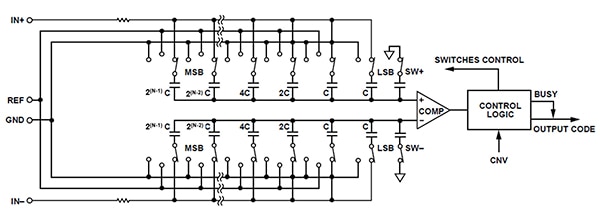

Ser på ADC's interiør ved hjælp af Analog Devices AD7915 (16-bit) og AD4021 (20-bit) SAR ADC'er som eksempler, kan det ses at bruge en digital-til-analog-konverter (DAC) til omfordeling af opladning. Den kapacitive DAC har to identiske arrays af binærvægtede kondensatorer. Disse arrays forbinder til de ikke-inverterende og inverterende komparatorindgange (figur 2).

Figur 2: En forenklet AD7915- og AD4021-baseret skematisk oversigt over en SAR ADC, hvor N er lig med konverterens antal bits. (Billedkilde: Modificeret af DigiKey fra originalt materiale fra Analog Devices)

Figur 2: En forenklet AD7915- og AD4021-baseret skematisk oversigt over en SAR ADC, hvor N er lig med konverterens antal bits. (Billedkilde: Modificeret af DigiKey fra originalt materiale fra Analog Devices)

Under erhvervelsesfasen skifter input (IN+ og IN-) til det kapacitive array. Derudover lukker SW+ og SW- og binder de mindst signifikante bit (LSB) kondensatorer til jord (GND). I denne tilstand bliver kondensatorarrays samplingskondensatorerne og erhverver IN+ og IN-analoge signaler. Efter afslutningen af erhvervelsesfasen går CNV-input til kontrollogikken (højre side) højt for at starte konverteringsfasen.

Konverteringsfasen begynder med åbningen af SW+ og SW- og skift af de to kondensatorarrays til GND. I denne konfiguration får den indfangede IN+ og IN- differentielle spænding komparatoren til at blive ubalanceret. Opladningsfordelingen DAC skifter metodisk hvert element i kondensatorarrayet fra mest signifikante bit (MSB) til LSB mellem GND og REF. Komparatorindgangen varierer efter binært vægtede spændingstrin (VREF/2N-1, VREF/2N-2 ... VREF/4, VREF/2). Kontrollogikken skifter switchene fra MSB til LSB, hvilket bringer komparatoren tilbage til en afbalanceret tilstand. Efter afslutningen af denne proces vender ADC tilbage til erhvervelsesfasen, og kontrollogikken genererer ADC-outputkoden.

Inputinjektion, kredsløbsstabilitet og kørsel af AD7915 ADC

En kritisk del af konverteringsprocessen er at erhverve en nøjagtig indgangssignalspænding. ADC-datakonvertering processen kører problemfrit, når drivforstærkeren nøjagtigt oplader indgangskondensatorerne, CIN+ og CI-, samtidig med at stabiliteten opretholdes til slutningen af ADC-erhvervelsestiden. Problemet for designere er, at ADC's indgangsterminal introducerer en kapacitans (CIN+, CI-) samt skiftende støj eller "kickback" opladningsindsprøjtning, som køreforstærkeren kan styre.

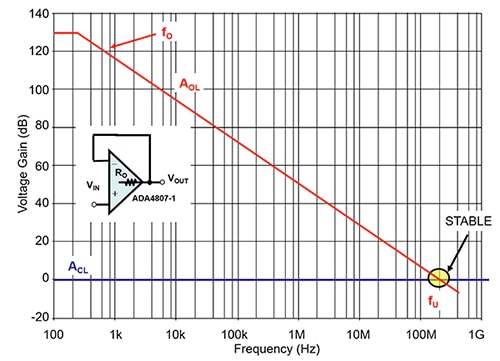

Et forstærkerkredsløb Bode-plot estimerer hurtigt kredsløbets stabilitet. Bode-plotværktøjet tilnærmer størrelsen af en forstærkers open-loop og systemets closed-loop-overførselsfunktioner (figur 3).

Figur 3: Den open og closed-loop-overføringsfunktion af forstærkeren i figur 1 uden Rext og Cext som forstærkerbelastninger og den følgende SAR ADC. (Billedkilde: DigiKey)

Figur 3: Den open og closed-loop-overføringsfunktion af forstærkeren i figur 1 uden Rext og Cext som forstærkerbelastninger og den følgende SAR ADC. (Billedkilde: DigiKey)

Y-aksen kvantificerer forstærkerens open-loop forstærkning (AOL) og forstærkning med closed-loop (ACL) af forstærkerkredsløbet, hvor forstærkerens AOL kurven starter ved 130 decibel (dB) og forstærkning med closed-loop, ACL, er lig med 0 dB. Enhederne langs x-aksen kvantificerer logaritmisk den open og closed loop-forstærkningsfrekvens fra 100 Hertz (Hz) til 1 gigahertz (GHz).

I figur 3 forstærker forstærkerens DC open-loop forstærkning ved ca. 220 Hz (fO) skrider nedad fra 130 dB med en hastighed på -20 dB/årti. Efterhånden som frekvensen øges, fortsætter denne dæmpningshastighed over 0 dB ved ca. 180 megahertz (MHz). Da denne kurve repræsenterer et enkeltpolet system, er delefrekvensen, fU, er lig med enhedsforstærkningsforstærkerens forstærkningsbåndbreddeprodukt (GBWP). Dette plot repræsenterer et stabilt system, fordi AOL og ACL lukningshastighed er 20 dB/årti.

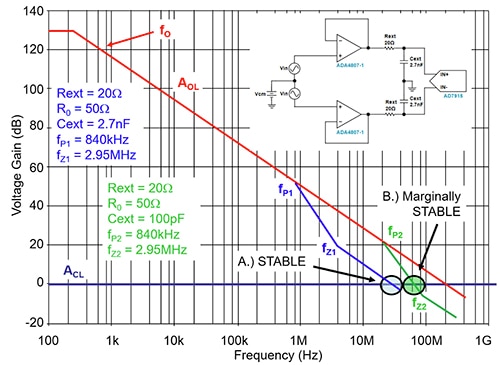

Tilføjelsen af Rext og Cext og SAR ADC ændrer forstærkerkredsløbet ved at oprette et system nul og pol (figur 4). Systemet består af en 16-bit, 1 megasample per sekund (MSPS) AD7915 differentiel PulSAR ADC og en 180 MHz, skinne-til-skinne input/output ADA4807-1 forstærker, begge fra Analog Devices. Kombinationen af forstærkeren og ADC kræver Rext på grund af 30 picofarad (pF) (typ) ADC input kapacitans belastning. Kredsløbet kræver også, at Cext fungerer som en opladningslager for at give tilstrækkelig opladning ved ADC-indgangen til nøjagtigt at matche indgangsspændingen.

Figur 4: vist er Bode-plotresponset fra to ADA4807 op-amps, der driver AD7915 SAR ADC med to separate Rext/Cext-par. FP1 og fZ1 hjørnefrekvenser ændrer forstærkerens open-loop-forstærkning og skaber et stabilt systemrespons. FP2 og fZ2 hjørnefrekvenser ændrer forstærkerens open-loop-forstærkning og skaber et marginalt stabilt svar. (Billedkilde: DigiKey)

Figur 4: vist er Bode-plotresponset fra to ADA4807 op-amps, der driver AD7915 SAR ADC med to separate Rext/Cext-par. FP1 og fZ1 hjørnefrekvenser ændrer forstærkerens open-loop-forstærkning og skaber et stabilt systemrespons. FP2 og fZ2 hjørnefrekvenser ændrer forstærkerens open-loop-forstærkning og skaber et marginalt stabilt svar. (Billedkilde: DigiKey)

Kredsløbet i figur 4 kan potentielt svinge på grund af ADC kapacitiv belastning og ADC's skifteladningsinjection, når den første erhvervelse finder sted. Den ekstra pol og nul, der oprettes af Rext/Cext-forstærkerens udgangskomponenter, sikrer et stabilt system, så open og cloosed-loop forstærkning er større end 20 dB/årti, hvilket giver en fasemargin mindre end 45 °. Denne konfiguration med fP2 og fZ2, skaber et ustabilt kredsløb.

For at forhindre ustabilitet, når designere vurderer forstærkerens open-loop forstærkningskurve med Rext og Cext i kredsløbet, skal designere medtage effekten af forstærkerens open-loop output-modstand, RO. Kombinationen af RO svarende til 50 ohm (W), ændrer Rext og Cext open-loop-responskurven ved at indføre en pol (fP, Ligning 1) og et nul (fZ, Ligning 2). Værdierne RO, Rext og Cext bestemmer hjørnefrekvensen for fP. Værdierne for Rext og Cext bestemmer nul-hjørnefrekvensen, fZ.

Ligning 1

Ligning 1

Ligning 2

Ligning 2

FP og fZ beregninger er:

fP1 = 842 kHz

fZ1 = 2,95 MHz

med: RO = 50 W

Rext = 20 W

Cext = 2,7 nanofarads (nF)

fP2 = 22,7 MHz

fZ2 = 79,5 MHz

med: RO = 50 W

Rext = 20 W

Cext = 0,1 nF

Ovenstående værdier for fP1 og fZ1 giver et stabilt system til AD7915 og ADA4807-1.

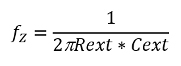

Kørsel af Easy Drive AD4021 SAR ADC

Et alternativ til AD7915 er AD4021 20-bit 1 MSPS Easy Drive SAR-konverter. AD4021-enhedsfamilien reducerer input-tilbageslag og inputstrøm i høj grad til 0,5 mikroampere (μA)/MSPS. Easy Drive har reduceret strømforbrug og kompleksitet i signalkæden.

AD4021s analoge indgang har kredsløb, der reducerer den typiske switchede kondensator SAR-indgang, ikke-lineær opladning. Tilbageslagsreduktionen og en længere erhvervelsesfase tillader brugen af driverforstærkere med lavere båndbredde og lavere effekt (figur 5).

Figur 5: Indgangskredsløbet og optagelsestimingen for AD4021 reducerer tilbageslagskiftestrømmen og lindrer driverforstærkerens strenge krav. (Billedkilde: Analog Devices)

Figur 5: Indgangskredsløbet og optagelsestimingen for AD4021 reducerer tilbageslagskiftestrømmen og lindrer driverforstærkerens strenge krav. (Billedkilde: Analog Devices)

Kombinationen af tilbageslagsreduktion og længere erhvervelsestid tillader også en større Rext-modstandsværdi i input-resistor-kondensatorfilteret (RC) og en tilsvarende mindre Cext-kondensator. Denne kombination af en mindre Cext-forstærkerbelastning forbedrer stabiliteten og sænker effekttab.

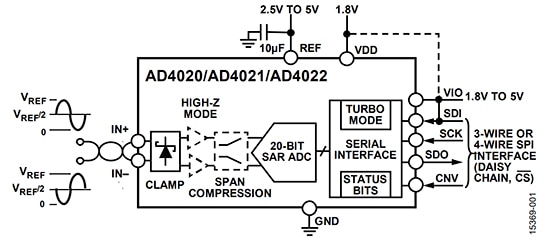

Det anbefalede forbindelsesdiagram til AD4021 ved hjælp af en enkelt 5 volt forsyning ser ud til at have et lignende kredsløbsdiagram. Forstærkerkravene er imidlertid afslappede, og Rext/Cext (R og C) -værdierne er mindre (figur 6).

Figur 6: Typisk AD4021- og ADA4807-1-applikationsdiagram, der drives af en enkelt 5 volt forsyning med mere afslappede forstærkerkrav og en større Rext-værdi sammenlignet med at køre AD7915 diskuteret tidligere. (Billedkilde: Analog Devices)

Figur 6: Typisk AD4021- og ADA4807-1-applikationsdiagram, der drives af en enkelt 5 volt forsyning med mere afslappede forstærkerkrav og en større Rext-værdi sammenlignet med at køre AD7915 diskuteret tidligere. (Billedkilde: Analog Devices)

I figur 6 bruger den SAR-baserede AD4021 også en ladningsomfordelingssampling DAC. ADC har et indbygget konverteringsur og serielt ur. Derfor kræver konverteringsprocessen ikke et synkron ur (SCK) input. Denne urkonfiguration muliggør forlængelse af optagelsestiden, hvilket forbedrer nøjagtigheden ved at give mere tid til indgangssignalet til at afregne til en endelig værdi.

Hovedhensynet til drevforstærkeren for både AD7915 og AD4021 er støj, da forstærker/Rext/Cext-kombinationen skal afregnes fra et trin i fuld skala til et 16-bit niveau (0,0015%, 15 ppm) for AD7915, og et 20-bit niveau (0,00001%, 1 ppm) til AD4021.

For at bevare signal-til-støj (SNR) -præstationen for AD7915 og AD4021 skal driverforstærkerens støj være mindre end en tredjedel af ADC's støj. AD4021-støj er 60 mikrovolt rms (mVrms), hvilket kræver, at forstærker/Rext/Cext-kombinationen er mindre end 20 mVrms. AD4021-støj er 31,5 mVrms, hvilket kræver, at forstærker/Rext/Cext-kombinationen er mindre end 10,5 mVrms.

Precision ADC Driver Værktøj fra Analog Devices hjælper designere med hurtigt at beregne de korrekte Rext- og Cext-værdier. Med en valgt driver og ADC modellerer dette værktøj kredsløbets afviklingstid, støj og forvrængningsadfærd.

Konklusion

SAR ADC fortsætter med at dominere applikationer med ultrahøj hastighed til dataindsamling, industriel kontrol og instrumentering. Imidlertid kræver det eksterne indgangskredsløb for disse enheder - drivforstærkeren og indgangsfilteret - særlig overvejelse for at imødekomme potentielle problemer med skiftladningsinjection og forstærkerstabilitet.

Løsningen til præcis indgangssignalstyring for de fleste SAR-omformere, såsom AD7916 og AD4021, ligger i op-amp-driveren - i dette tilfælde ADA4807-1. Som vist danner disse enheder, understøttet af de korrekte outputmodstands- og kondensatorværdier, et solidt fundament, hvorpå man kan bygge et højpræcisions, robust, 16-bit eller 20-bit SAR-konverteringssystem med høj opløsning.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.