Extending the Life of Sensor Nodes through Power-Efficient Design

Contributed By DigiKey's European Editors

2018-01-04

IoT nodes require operation for many years without a primary battery change in order to keep maintenance to a minimum. Some types of systems even make it possible to operate with very little battery power, relying on an energy harvester such as a solar array or small turbine to provide the long-term power requirements.

The fundamental drawback of energy harvesting designs is that the source of power is not reliable except in cases such as flow meters where the movement of fluid is expected to be continuous, and the harvester can absorb some of the kinetic energy from that flow.

In most cases, the best that the harvester can achieve is a flow of energy at low continuous levels. Very often there are peaks and troughs in delivery that, unfortunately, are unlikely to coincide with the peak demands of the system. This calls for the storage of temporarily excess energy within a reservoir within the system, using a component such as a rechargeable battery or capacitor.

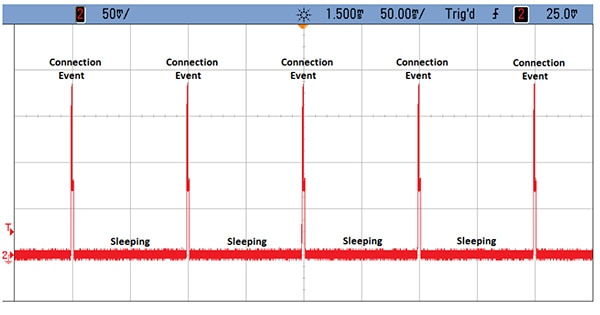

If the system is able to remain quiescent for long periods of time, it allows the flow of small amounts of energy to accumulate enough to drive peak demand. Such peak demand spikes are common to IoT node design, as shown in Figure 1. Such nodes achieve low overall energy targets by ensuring much of their circuitry is powered down while they are inactive. Such low duty cycle behavior makes it possible to design systems where for no more than one percent of the system’s lifetime is it in a high-power state.

Figure 1: Power usage characteristic of typical IoT sensor node.

Within the energy envelope, an IoT node needs to be able to perform a number of tasks. Typically, the node will sense incoming data such as flow rates within a pipe, or in the case of an environmental sensor, temperature or moisture levels. The system will need to transfer data it receives to a peer or server to allow comparison with other nodes’ reports, and to take action if the data indicates significant changes. If a comparison or filter algorithm shows a reportable change, it will need to activate an RF transceiver, assemble a packet of data, and send it to the IoT gateway. It will also need to listen for acknowledgements as well as network status updates.

It is likely that peak power will be during RF transmissions. However, it is possible to sequence activity such that a packet is assembled and passed to the RF subsystem first, allowing parts of the node to shut down, before initiating the actual RF transfer. This helps smooth out power peaks and prevents situations where the capacitor and battery combination are discharged too quickly.

There are simple circuit design techniques that allow charging a reservoir capacitor from an energy harvester to provide enough power to support the demands of activity peaks. One is based on a diode in series with the solar cell or similar harvester and the supply rail. The capacitor can charge up to the open-circuit voltage of the harvester. Overvoltage protection in parallel protects the capacitor and power rail from being pushed to too high of a voltage level. However, this only works in situations where the solar cell array can develop a higher voltage than the supply rail. Many small-scale generators, and those based on alternative harvesting techniques such as thermoelectric generation, will never approach this level. Also, charging to a maximum voltage does not fit with solar generation, where the voltage at the current maximum power point (MPP) varies with illumination intensity.

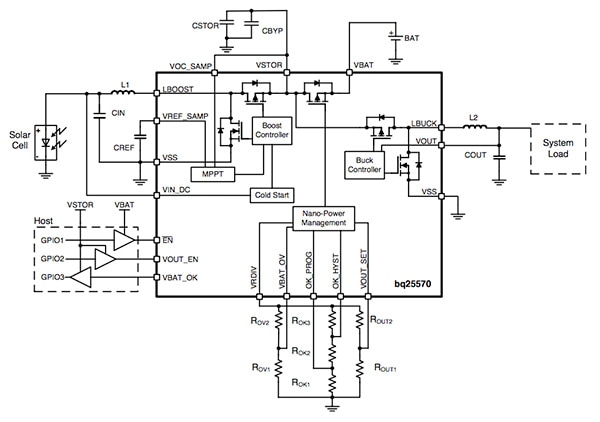

What is required is a specialized device that is able to manage the capacitor and system voltage. The Texas Instruments (TI) BQ25570 power management integrated circuit (PMIC) is designed to make it possible to extract microwatt to milliwatt levels of power from a variety of harvesting sources, most of which tend to be low-voltage sources with high output impedance. The battery management features ensure that any attached rechargeable battery or reservoir capacitor is not overcharged by this extracted power, allowing safe operation with lithium-based cells. It also ensures the battery is not depleted beyond safe limits by a system load. In addition to the highly efficient boosting charger, the BQ25570 provides an ultra-low power buck converter for providing a second power rail to the system.

The BQ25570 performs MPP tracking by regulating the charger's input voltage which is sensed by VIN_DC as shown on the block diagram in Figure 2. This is compared to a sampled reference voltage at the VREF_SAMP pin. The MPP tracking circuit obtains a new reference voltage every 16 seconds by periodically disabling the charger for approximately 250 ms and sampling a fraction of the open-circuit voltage. For solar harvesters, the MPP is typically between 70 and 80 percent, and around 50 percent for thermoelectric harvesters. The BQ25570 is programmed to these levels by tying the VOC_SAMP to the reservoir capacitor (VSTOR) or to ground for solar and thermoelectric sources, respectively. If the input source does not have either 80 percent or 50 percent as its MPP point, the exact ratio can be programmed by connecting external resistors between the VRDIV and ground pins.

Figure 2: Block diagram of the BQ25570 in a typical solar-powered circuit.

Rechargeable batteries or reservoir capacitors are protected from overvoltage or overcharging conditions by setting a peak threshold on the VBAT_OV pin using external resistors. This setting also functions as the voltage provided by the charger to the system when the harvester input has sufficient power to drive it.

Reservoir capacitor choices will be driven partly by overall size and also by leakage considerations. The highest capacities available are from electrochemical “supercapacitors”, which can be obtained in sizes up to 50 F. However, they suffer from high leakage levels that make them unsuitable for designs where energy harvesting opportunities are intermittent. A better choice may be a tantalum capacitor, although care needs to be taken in designs where fire resistance is a concern. These offer reasonably high capacitance levels together with leakage in the nano amp range. An overall balance of cost, safety, and low leakage favors ceramic capacitors, although these are limited to a capacitance of around half a millifarad.

To help with the management of energy budgets, the BQ25570 controls the battery good (VBAT_OK) flag. This signals an attached microprocessor when the voltage on an energy storage battery or capacitor has dropped below a preset critical level. This can be used to start the reduction of load currents to prevent the system from entering an undervoltage condition. Enable signals let the MCU control the state of the PMIC, and where necessary, put it into an ultra-low quiescent current sleep state to further save energy.

With many low duty-cycle systems, the MCU can move into a deep sleep state where power consumption is cut to very low levels. However, there may be situations where the system is unable to continue because it has temporarily run out of reserve power. It is possible to design systems to not just tolerate these situations, but regard them as normal and use techniques to avoid requiring a full reboot. These system designs help make energy harvesting a more viable technique.

Many MCUs rely on backup memory cells to hold key data during hibernation. If they are based on SRAM, retention cells will incur some leakage and will lose their contents if power is interrupted. Writing data periodically to flash memory partially overcomes the problem. However, there is an issue if an imminent power failure is signaled without sufficient power to support the high current levels needed to perform a set of flash writes. To support writes to flash, an MCU normally requires an integrated charge pump to complete erase-and-write sequences, often requiring 5 mA to 10 mA for several hundred milliseconds.

An alternative is for the MCU to power down entirely and to reboot on the restoration of power, and then attempt to recover its state from persistent storage, or from the server by downloading state information it provided before shutting down. This, however, increases power consumption significantly and can lead to situations where if sufficient energy has not been accumulated by the PMIC and capacitor, the node suffers a succession of failed reboots. By storing temporary data, the system avoids the need for a reboot. The more detailed the information on a system state, the less recovery the system needs to perform to ensure it is ready to operate correctly.

Ferroelectric Random Access Memory (FRAM) provides a memory technology that makes it possible to store large quantities of temporary data through power outages in systems with highly limited power envelopes. A major benefit of FRAM is its support for ultra-low-power writes. This is a benefit seen in two different ways. Unlike flash, writes to FRAM require no pre-erase cycle. The write itself demands far lower charges than flash.

FRAM has a similar construction to DRAM, based around a capacitive storage element. This is generally combined with a programming transistor. Whereas flash uses high electric fields to store charge within the insulator of a floating gate in a transistor, the ferroelectric capacitor stores the charge within the capacitor. Unlike a conventional capacitor, the material is chosen such that it forms semi-permanent electric dipoles in its crystal structure when a programming charge is applied. Reading is destructive, as it forces the cell to an empty state. However, the write is of such low power it can easily be performed after each successful read to replace the original value if a ‘1’, or to load a new ‘1’.

The TI MSP430FRx series of MCUs include up to 128 KB of on-chip FRAM for the persistent storage of data. The MCUs support ultra-low-power states where the on-chip memory arrays and registers are not powered, but the FRAM will continue to store its contents.

The Compute Through Power Loss (CTPL) software utility provides system designers with an easy way to leverage FRAM for use as a persistent state storage function. The library provides a number of application programming interfaces (APIs) to monitor for events such as a power failure, and react to them. Typically, the software library will transfer state data from SRAM and registers to FRAM before power is removed from the system.

When power is restored, the CPTL library allows FRAM contents to be transferred back to SRAM data structures and MCU registers to allow continued execution.

Further power optimizations can be obtained by architecting the system software to minimize the number of full wakeup periods. Designs will usually separate into two broad classes: reactive and periodic. Reactive operation puts the system into a standby state to wait for some activity or event before initiating processing and then returning to a deep sleep.

The activity may be tied to the harvesting function itself. For example, in a system powered by vibration or motion harvesting, any large movement will not only provide energy but also activate the sensor node to take a recording. For example, a bridge vibration monitor can use this activity to drive its operation taking measurements when heavy vehicles or winds that disturb the structure are imparting high stresses.

In contrast, periodic systems wake up after a fixed interval and perform a measurement. If the data reaches a level that needs attention, the system can process and potentially relay the information over the network before re-entering sleep mode. Although more wasteful of energy than a purely reactive system design, the periodic architecture is often needed for situations where it is difficult to simply use an activity threshold to determine whether an input requires attention. Inductive flow sensing is one example.

However, with MCUs such as the MSP430RFx it is possible to ameliorate the energy consumption. The 10-bit ADC on a device such as the MSP420FR413x can be triggered to operate independently of the CPU core. The real-time clock can start an acquisition after a defined period. A window comparator with an upper and lower limit can then determine whether the CPU needs to be woken for further analysis. This limits the number of full wakeups required during the lifetime of the sensor node.

Conclusion

As a result, the MSP430 can provide the heart of an ultra-high-efficiency reactive or periodic IoT sensor node, using energy harvesting enabled by the BQ25570 PMIC to further extend the life of the system beyond what is possible with a pure battery-based design.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.